ZL30414

ZL30414 is SONET/SDH Clock Multiplier PLL manufactured by Zarlink Semiconductor.

..

ZL30414 SONET/SDH Clock Multiplier PLL

Data Sheet Features

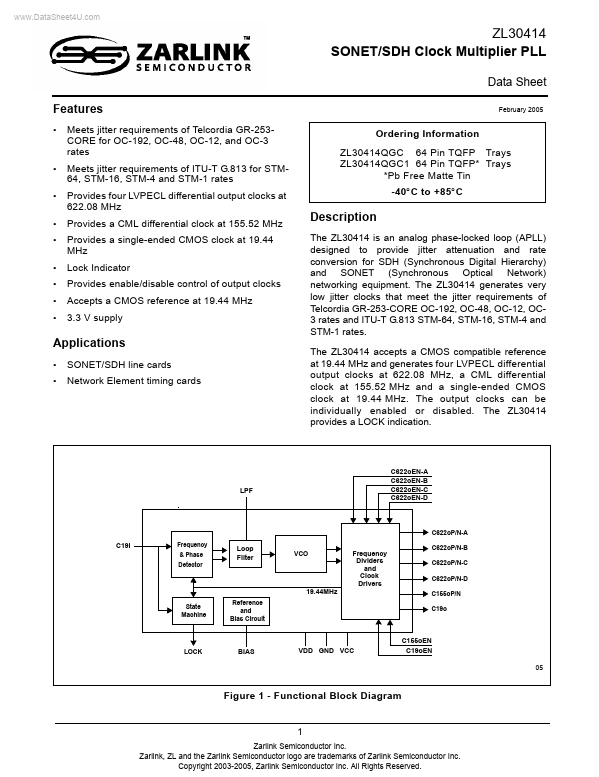

- Meets jitter requirements of Telcordia GR-253CORE for OC-192, OC-48, OC-12, and OC-3 rates Meets jitter requirements of ITU-T G.813 for STM64, STM-16, STM-4 and STM-1 rates Provides four LVPECL differential output clocks at 622.08 MHz Provides a CML differential clock at 155.52 MHz Provides a single-ended CMOS clock at 19.44 MHz Lock Indicator Provides enable/disable control of output clocks Accepts a CMOS reference at 19.44 MHz 3.3 V supply Ordering Information ZL30414QGC 64 Pin TQFP Trays ZL30414QGC1 64 Pin TQFP- Trays

- Pb Free Matte Tin -40° C to +85 ° C

February 2005

- -

- -

- -

- -

Description

The...