ZL30415

ZL30415 is SONET/SDH Clock Multiplier PLL manufactured by Zarlink Semiconductor.

Features

- -

- Meets jitter requirements of Telcordia GR-253CORE for OC-12, OC-3, and OC-1 rates Meets jitter requirements of ITU-T G.813 for STM4, and STM-1 rates Provides one differential LVPECL output clock selectable to 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, or 622.08 MHz Provides a single-ended CMOS output clock at 19.44 MHz Accepts a single-ended CMOS reference at 19.44 MHz or a differential LVDS, LVPECL, or CML reference at 19.44 MHz or 77.76 MHz Provides a LOCK indication 3.3 V supply Ordering Information ZL30415GGC 64 Ball CABGA

November 2004

-40°C to +85 °C

- -

Description

The ZL30415 is an analog phase-locked loop (APLL) designed to provide jitter attenuation and rate conversion for SDH (Synchronous Digital Hierarchy) and SONET (Synchronous Optical Network) networking equipment. The ZL30415 generates low jitter output clocks that meet the jitter requirements of Telcordia GR-253-CORE OC-12, OC-3, OC-1 rates and ITU-T G.813 STM-4 and STM-1 rates. The ZL30415 accepts a CMOS patible reference at 19.44 MHz or a differential LVDS, LVPECL, or CML reference at 19.44 MHz or 77.76 MHz and generates a differential LVPECL output clock selectable to 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz, or 622.08 MHz, and a single-ended CMOS clock at 19.44 MHz. The ZL30415 provides a lock indication.

- -

Applications

- SONET/SDH line cards

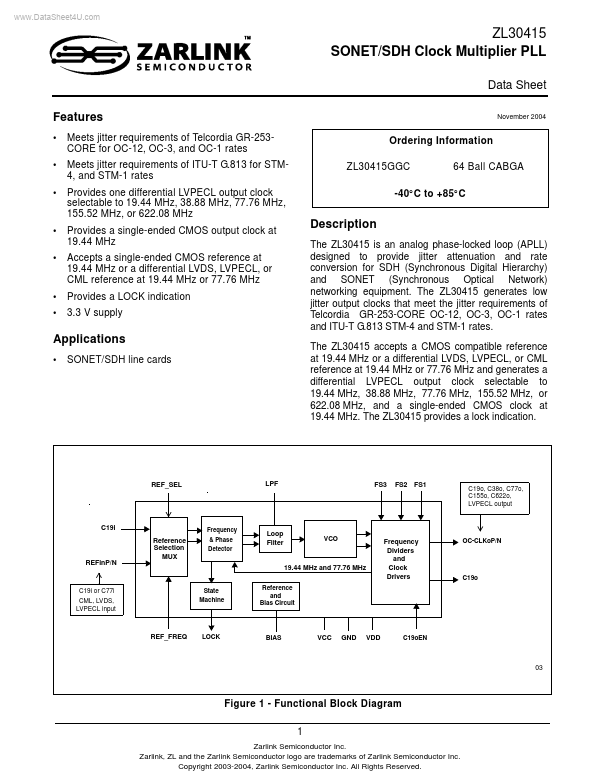

REF_SEL

FS3

FS2 FS1

C19o, C38o, C77o, C155o, C622o, LVPECL output

C19i Reference Selection MUX

Frequency & Phase Detector

Loop Filter

REFin P/N

19.44 MHz and 77.76 MHz State Machine Reference and Bias Circuit

Frequency Dividers and Clock Drivers

OC-CLKo P/N

C19o

C19i or C77i CML, LVDS, LVPECL input

REF_FREQ

LOCK

BIAS

C19o EN

Figure 1

- Functional Block Diagram 1

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2003-2004, Zarlink Semiconductor Inc. All Rights Reserved.

Data Sheet

1...