ZL30416

Description

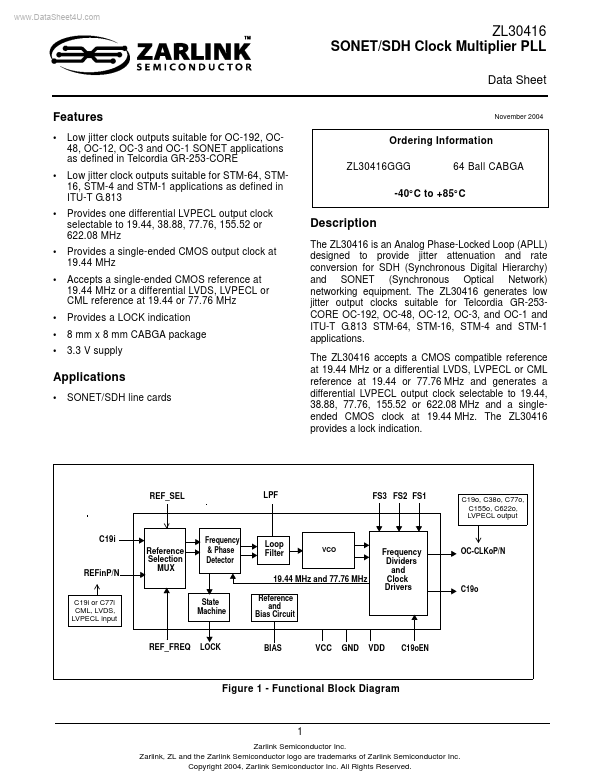

The ZL30416 is an Analog Phase-Locked Loop (APLL) designed to provide jitter attenuation and rate conversion for SDH (Synchronous Digital Hierarchy) and SONET (Synchronous Optical Network) networking equipment. The ZL30416 generates low jitter output clocks suitable for Telcordia GR-253CORE OC-192, OC-48, OC-12, OC-3, and OC-1 and ITU-T G.813 STM-64, STM-16, STM-4 and STM-1 applications.

Key Features

- Low jitter clock outputs suitable for OC-192, OC48, OC-12, OC-3 and OC-1 SONET applications as defined in Telcordia GR-253-CORE Low jitter clock outputs suitable for STM-64, STM16, STM-4 and STM-1 applications as defined in ITU-T G.813 Provides one differential LVPECL output clock selectable to 19.44, 38.88, 77.76, 155.52 or 622.08 MHz Provides a single-ended CMOS output clock at 19.44 MHz Accepts a single-ended CMOS reference at 19.44 MHz or a differential LVDS, LVPECL or CML reference at 19.44 or 77.76 MHz Provides a LOCK indication 8 mm x 8 mm CABGA package 3.3 V supply Ordering Information ZL30416GGG 64 Ball CABGA November 2004

- -40°C to +85 °C