ZL50418 Overview

ZL50418 Managed 16-Port 10/100 M + 2-Port 1 G Ethernet Switch Data Sheet.

ZL50418 Key Features

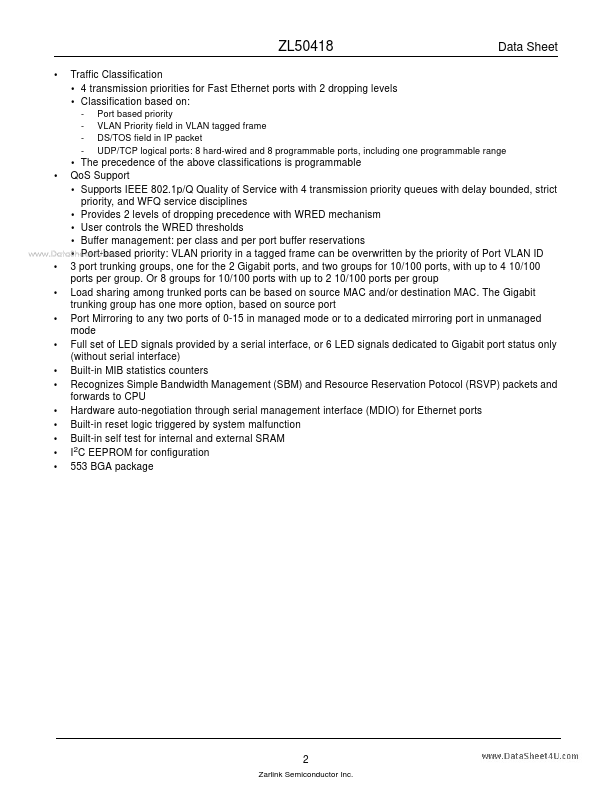

- 16 10/100 Mbps Autosensing, Fast Ethernet Ports with RMII or Serial Interface (7WS). Each port can independently use one

- 2 Gigabit Ports with GMII, PCS and 10/100 interface options per port

- Gigabit port supports hot swap in managed configuration

- Supports 8/16-bit CPU interface in managed mode

- Serial interface in unmanaged mode

- Supports two Frame Buffer Memory domains with SRAM at 100 MHz

- Supports memory size 2 MB, or 4 MB

- Two SRAM domains (2 MB or 4 MB) are required

- Applies centralized shared memory architecture

- Up to 64 K MAC addresses