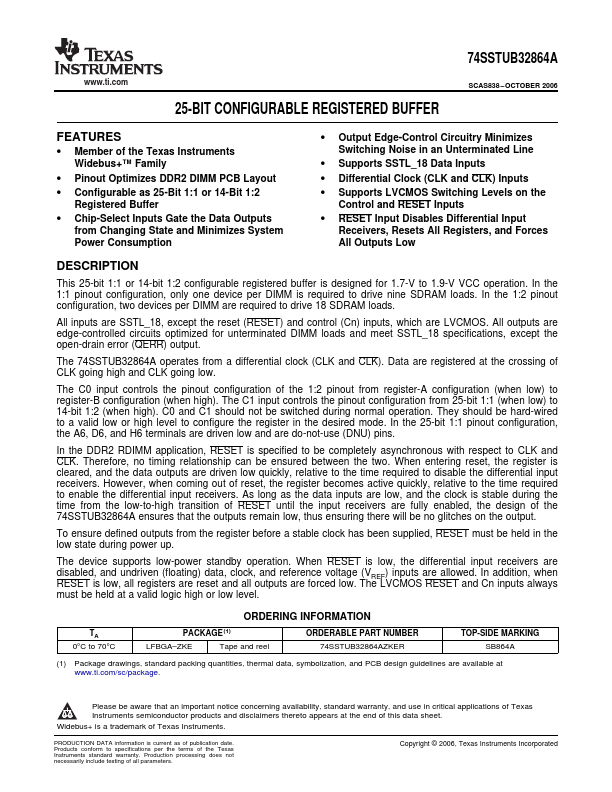

74SSTUB32864A

Description

This 25-bit 1:1 or 14-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VCC operation.

Key Features

- Member of the Texas Instruments Widebus+™ Family

- Pinout Optimizes DDR2 DIMM PCB Layout

- Chip-Select Inputs Gate the Data Outputs from Changing State and Minimizes System Power Consumption

- Output Edge-Control Circuitry Minimizes Switching Noise in an Unterminated Line

- Supports SSTL_18 Data Inputs

- Differential Clock (CLK and CLK) Inputs

- Supports LVCMOS Switching Levels on the

- RESET Input Disables Differential Input Receivers, Resets All Registers, and Forces All Outputs Low