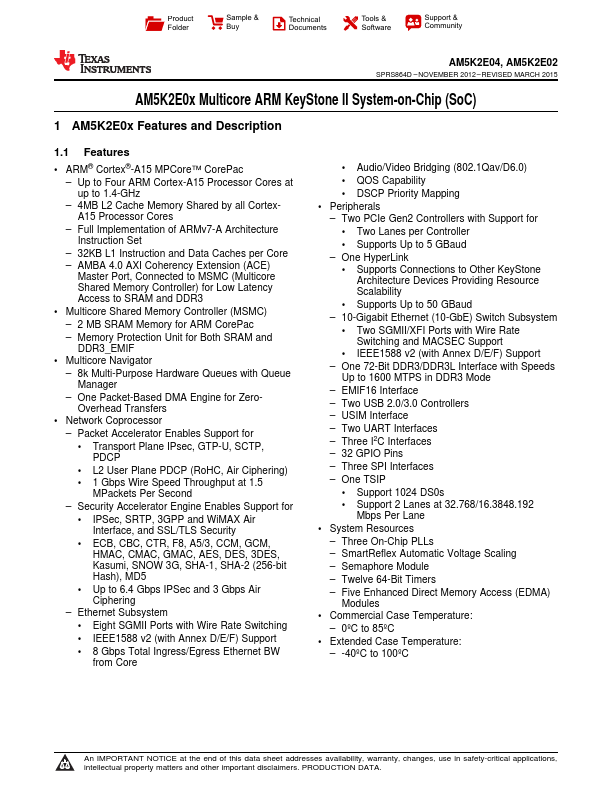

AM5K2E02 Overview

Key Specifications

Package: FCBGA

Pins: 1089

Length: 27 mm

Width: 27 mm

Key Features

- Multicore Shared Memory Controller (MSMC) – 2 MB SRAM Memory for ARM CorePac – Memory Protection Unit for Both SRAM and DDR3_EMIF

- Multicore Navigator – 8k Multi-Purpose Hardware Queues with Queue Manager – One Packet-Based DMA Engine for ZeroOverhead Transfers

- Network Coprocessor – Packet Accelerator Enables Support for

- Transport Plane IPsec, GTP-U, SCTP, PDCP

- L2 User Plane PDCP (RoHC, Air Ciphering)