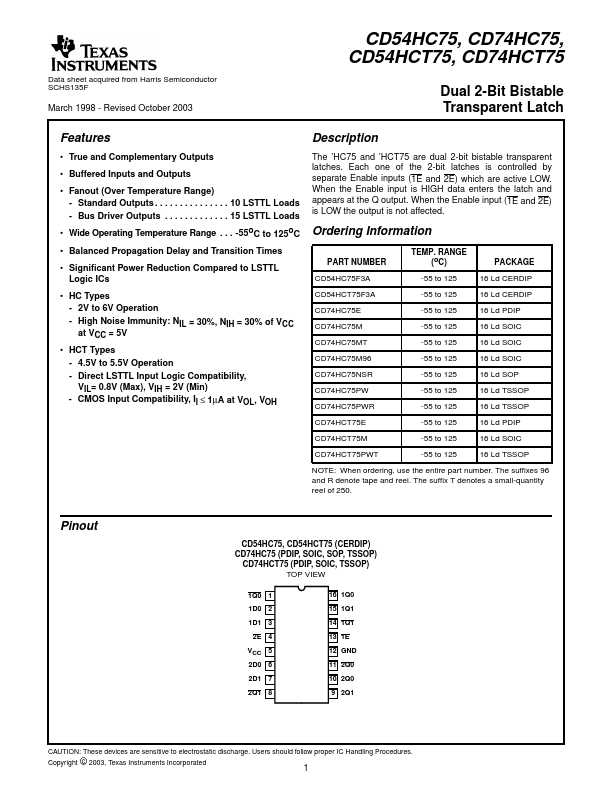

| Part | CD54HC75F3A |

|---|---|

| Description | Dual 2-Bit Bistable Transparent Latch |

| Manufacturer | Texas Instruments |

| Size | 785.62 KB |

Pricing from 23.451 USD, available from Texas Instruments and Component Stockers USA.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Texas Instruments | 0 | 1+ : 23.451 USD 100+ : 20.484 USD 250+ : 15.794 USD 1000+ : 14.127 USD |

View Offer |

| Component Stockers USA | 10437 | 1+ : 8.26 USD 10+ : 8.1 USD 100+ : 7.85 USD 1000+ : 7.6 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AH477A | BCD Semiconductor | SINGLE PHASE HALL EFFECT LATCH |

| SS41F | SEC | Hall Latch Position Sensor |

| 9314 | National Semiconductor | Quad Latch |