CD54HCT132 Overview

Key Specifications

Package: CDIP

Mount Type: Through Hole

Pins: 14

Operating Voltage: 5 V

Description

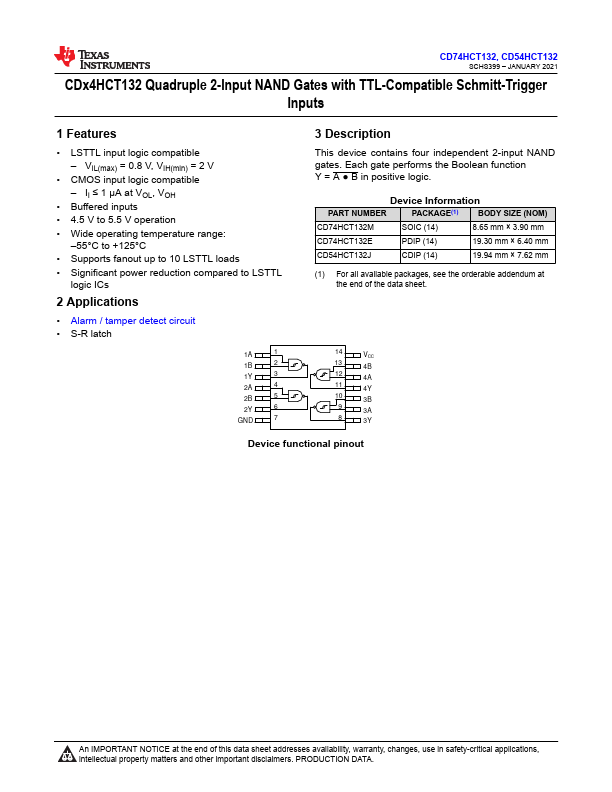

This device contains four independent 2-input NAND gates. Each gate performs the Boolean function Y = A - B in positive logic.

Key Features

- LSTTL input logic compatible – VIL(max) = 0.8 V, VIH(min) = 2 V

- CMOS input logic compatible – II ≤ 1 µA at VOL, VOH

- Buffered inputs

- 4.5 V to 5.5 V operation

- Wide operating temperature range: –55°C to +125°C