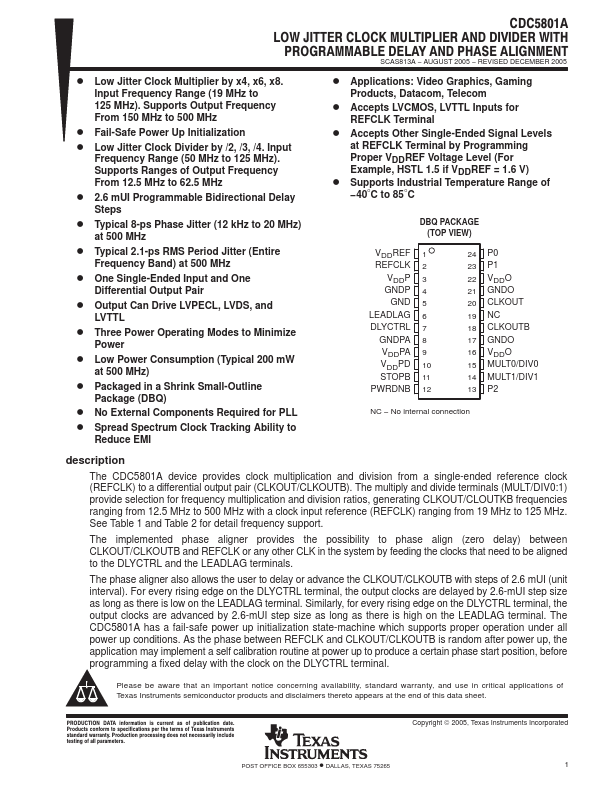

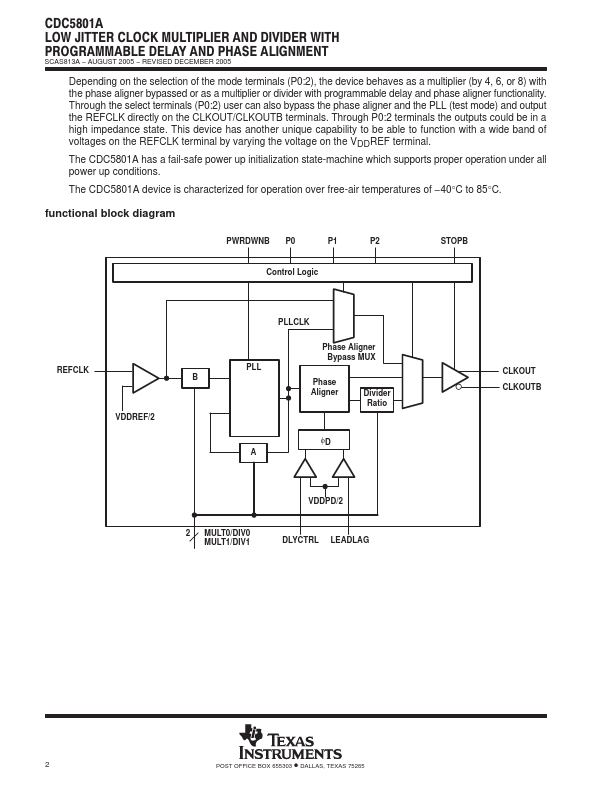

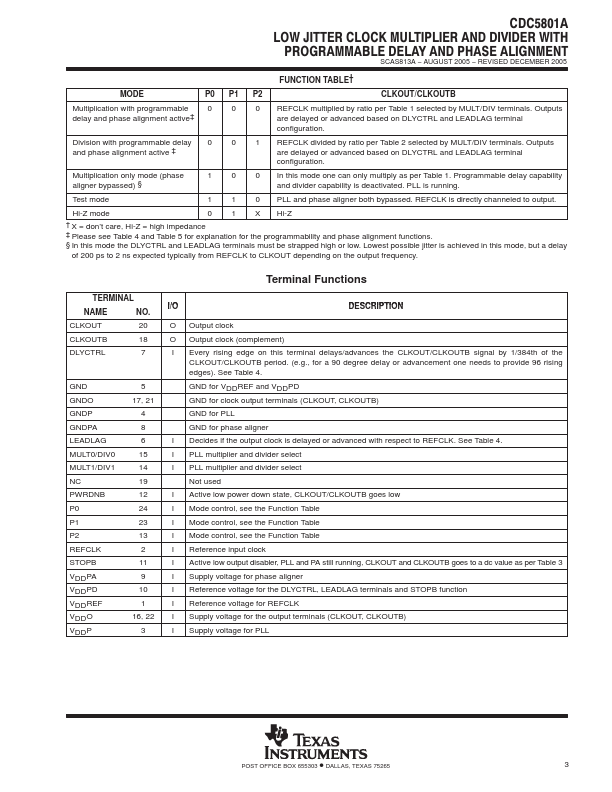

Datasheet Summary

CDC5801A LOW JITTER CLOCK MULTIPLIER AND DIVIDER WITH

PROGRAMMABLE DELAY AND PHASE ALIGNMENT SCAS813A

- AUGUST 2005

- REVISED DECEMBER 2005

D Low Jitter Clock Multiplier by x4, x6, x8.

Input Frequency Range (19 MHz to 125 MHz). Supports Output Frequency From 150 MHz to 500 MHz

D Fail-Safe Power Up Initialization D Low Jitter Clock Divider by /2, /3, /4. Input

Frequency Range (50 MHz to 125 MHz). Supports Ranges of Output Frequency From 12.5 MHz to 62.5 MHz

D 2.6 mUI Programmable Bidirectional Delay

Steps

D Typical 8-ps Phase Jitter (12 kHz to 20 MHz) at 500 MHz

D Typical 2.1-ps RMS Period Jitter (Entire

Frequency Band) at 500 MHz

D One Single-Ended Input and One

Differential Output...