Datasheet Summary

Not Remended for New Designs

.ti.

SCAS698F

- SEPTEMBER 2003

- REVISED APRIL 2006

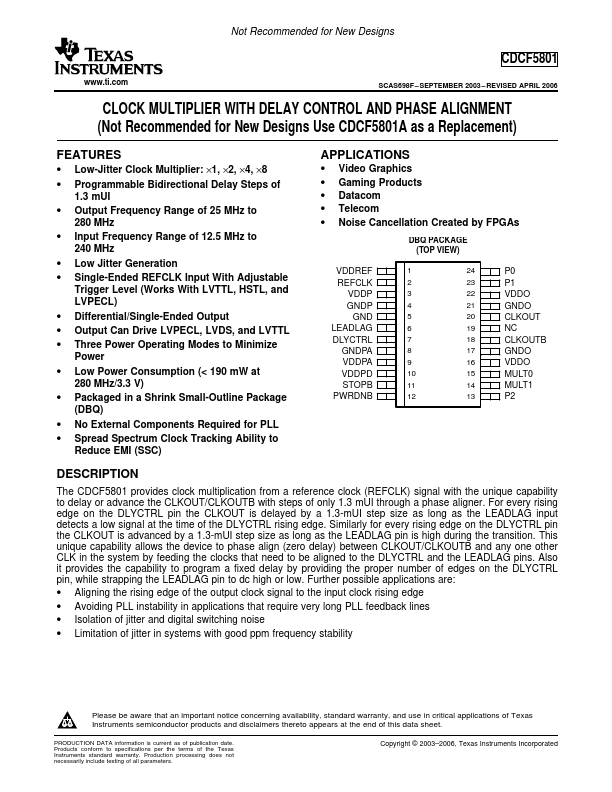

CLOCK MULTIPLIER WITH DELAY CONTROL AND PHASE ALIGNMENT (Not Remended for New Designs Use CDCF5801A as a Replacement)

Features

- Low-Jitter Clock Multiplier: ×1, ×2, ×4, ×8

- Programmable Bidirectional Delay Steps of

1.3 mUI

- Output Frequency Range of 25 MHz to 280 MHz

- Input Frequency Range of 12.5 MHz to 240 MHz

- Low Jitter Generation

- Single-Ended REFCLK Input With Adjustable

Trigger Level (Works With LVTTL, HSTL, and LVPECL)

- Differential/Single-Ended Output

- Output Can Drive LVPECL, LVDS, and LVTTL

- Three Power Operating Modes to Minimize

Power

- Low Power Consumption (<...