Datasheet Summary

Product Folder

Order Now

Technical Documents

Tools & Software

Support & munity

SCAS759C

- APRIL 2004

- REVISED JULY 2017

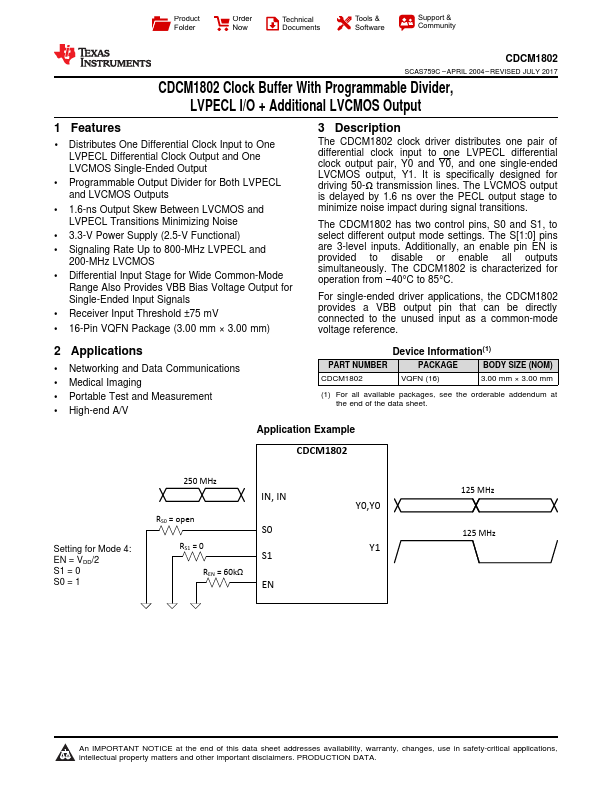

CDCM1802 Clock Buffer With Programmable Divider, LVPECL I/O + Additional LVCMOS Output

1 Features

- 1 Distributes One Differential Clock Input to One LVPECL Differential Clock Output and One LVCMOS Single-Ended Output

- Programmable Output Divider for Both LVPECL and LVCMOS Outputs

- 1.6-ns Output Skew Between LVCMOS and LVPECL Transitions Minimizing Noise

- 3.3-V Power Supply (2.5-V Functional)

- Signaling Rate Up to 800-MHz LVPECL and

200-MHz LVCMOS

- Differential Input Stage for Wide mon-Mode

Range Also Provides VBB Bias Voltage Output for...