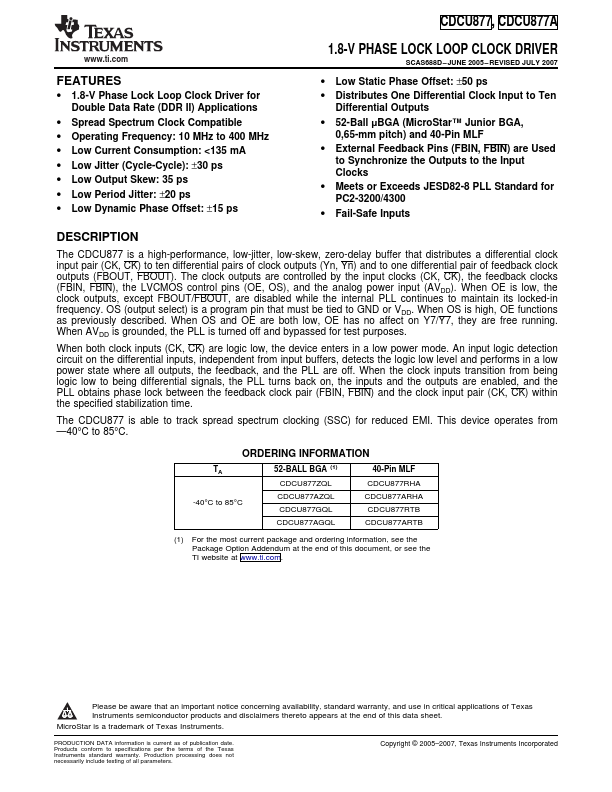

CDCU877A

Description

The CDCU877 is a high-performance, low-jitter, low-skew, zero-delay buffer that distributes a differential clock input pair (CK, CK) to ten differential pairs of clock outputs (Yn, Yn) and to one differential pair of feedback clock outputs (FBOUT, FBOUT).

Key Features

- 1.8-V Phase Lock Loop Clock Driver for Double Data Rate (DDR II) Applications

- Operating Frequency: 10 MHz to 400 MHz

- Low Current Consumption: <135 mA

- Low Jitter (Cycle-Cycle): ±30 ps

- Low Output Skew: 35 ps

- Low Period Jitter: ±20 ps

- Low Dynamic Phase Offset: ±15 ps

- Low Static Phase Offset: ±50 ps

- Distributes One Differential Clock Input to Ten

- 52-Ball μBGA (MicroStar™ Junior BGA