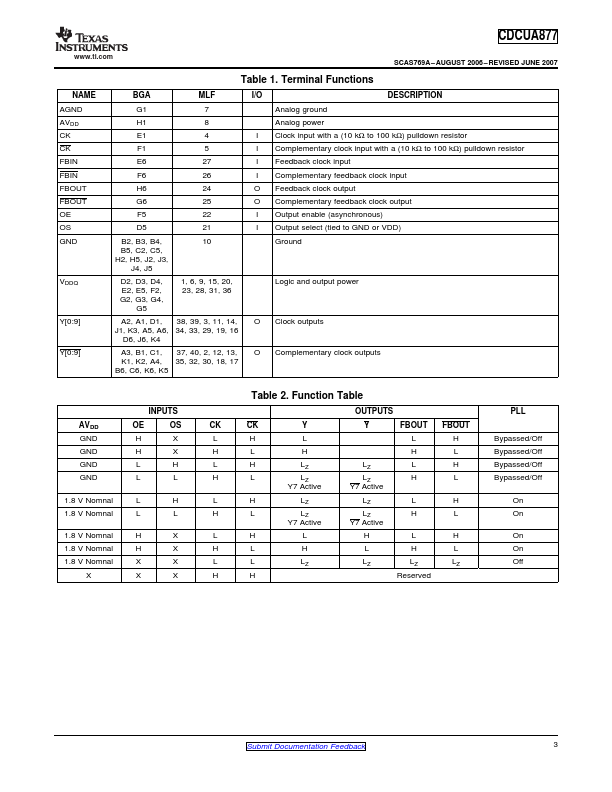

Datasheet Summary

.ti.

SCAS769A

- AUGUST 2006

- REVISED JUNE 2007

1.8-V PHASE LOCK LOOP CLOCK DRIVER

Features

- 1.8-V/1.9-V Phase Lock Loop Clock Driver for Double Data Rate (DDR II) Applications

- Spread Spectrum Clock patible

- Operating Frequency: 125 MHz to 410 MHz

- Application Frequency: 160 MHz to 410 MHz

- Low Current Consumption: <200 mA Typ

- Low Jitter (Cycle-Cycle): ±40 ps

- Low Output Skew: 35 ps

- Stabilization Time <6 μs

- Distributes One Differential Clock Input to Ten Differential Outputs

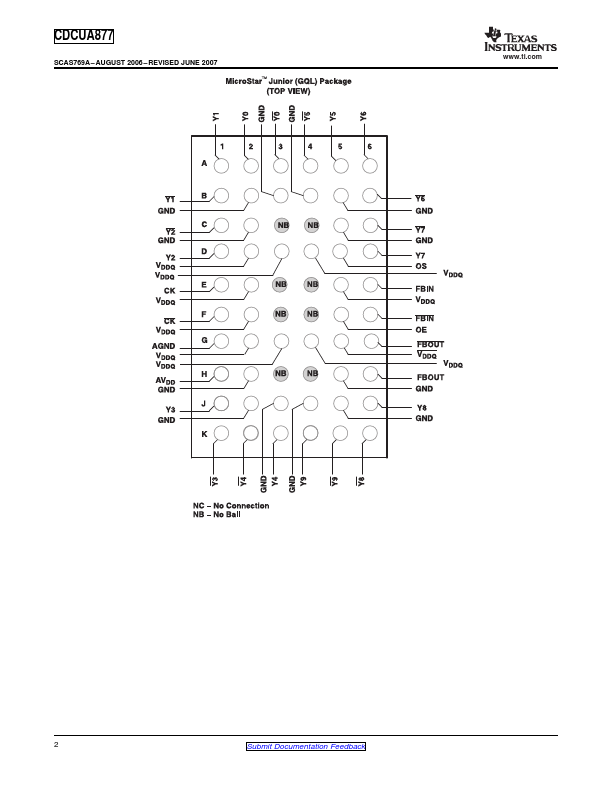

- 52-Ball μBGA (MicroStar Junior™ BGA, 0,65-mm pitch)

- External Feedback Pins (FBIN, FBIN) are Used to Synchronize the Outputs to the Input Clockst

- Meets or Exceeds CUA877/CAU878...