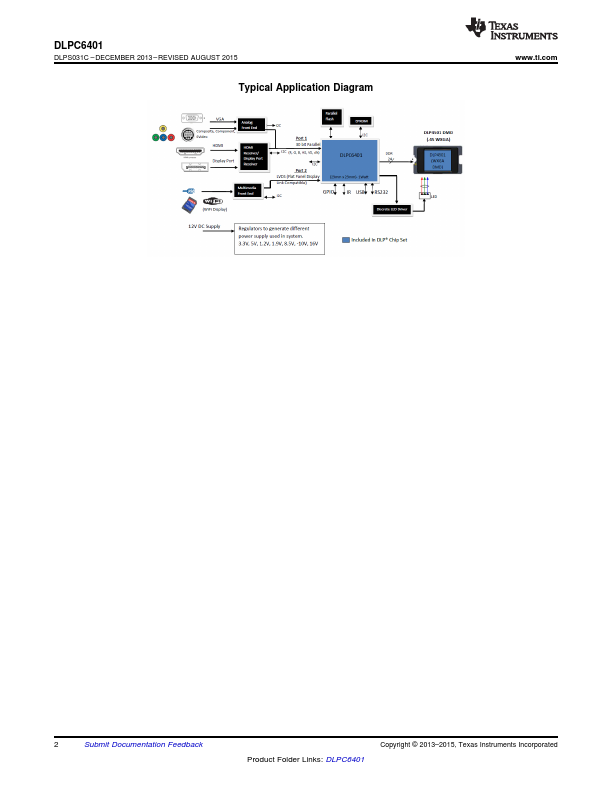

DLPC6401 Description

The DLPC6401 digital controller, part of the DLP4500 (.45 WXGA) chipset, supports reliable operation of the DLP4500 digital micromirror device (DMD). The DLPC6401 controller provides a convenient, multifunctional interface between system electronics and the DMD, enabling small form factor and high resolution HD displays. Device Information (1) PART NUMBER PACKAGE ARRAY SIZE (PIXELS) DLPC6401 BGA (419) 23.00 mm ×...

DLPC6401 Key Features

- 1 Provides a 30-Bit Input Pixel Interface

- YUV, YCrCb, or RGB Data Format

- 8, 9, or 10 Bits per Color

- Pixel Clock Support up to 150 MHz

- Provides a Single Channel, LVDS Based, Flat-Panel Display (FPD)-Link patible Input Interface

- Supports Sources up to a 90-MHz Effective Pixel Clock Rate

- Four Demodulated Pixel-Mapped Modes Supported for 8, 9, 10 YUV, YCrCb, or RGB Formatted Inputs

- Supports 45- to 120-Hz Frame Rates

- Full Support for Diamond 0.45 WXGA

- High-Speed, Double Data Rate (DDR) Digital