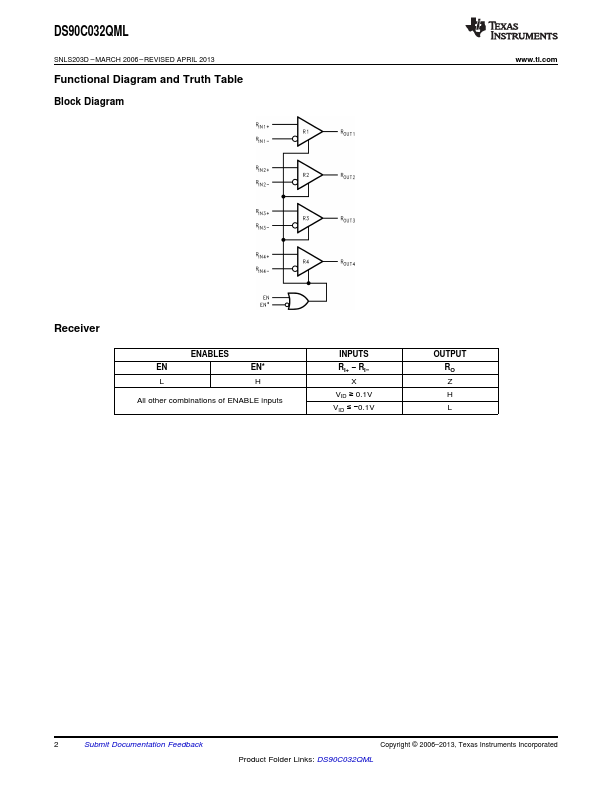

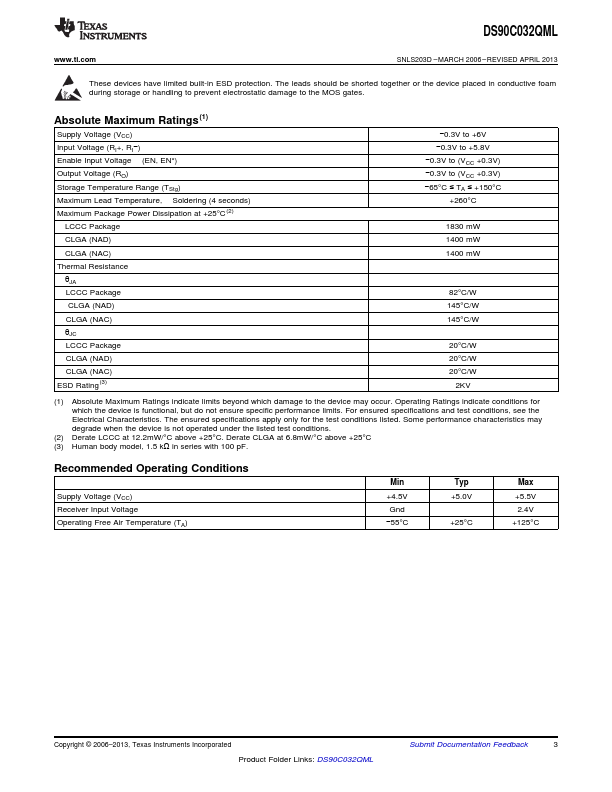

Datasheet Summary

.ti.

SNLS203D

- MARCH 2006

- REVISED APRIL 2013

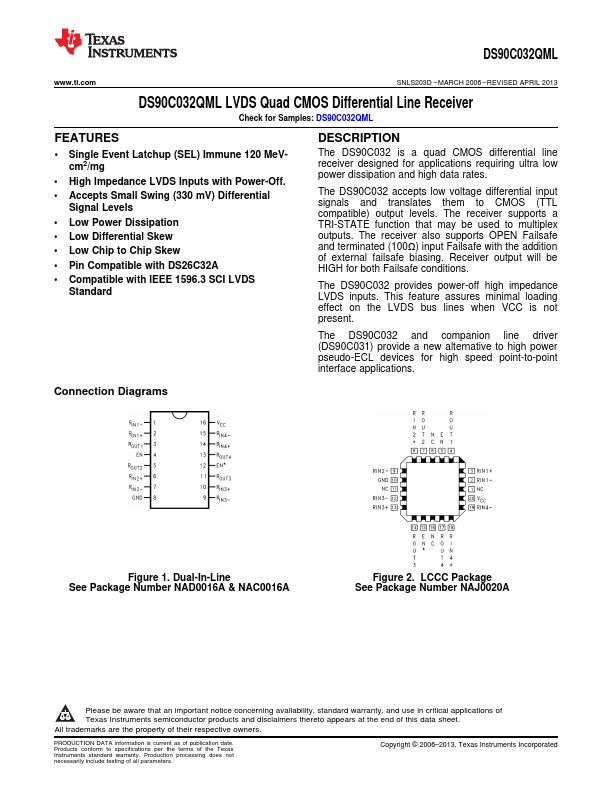

DS90C032QML LVDS Quad CMOS Differential Line Receiver

Check for Samples: DS90C032QML

Features

- 2 Single Event Latchup (SEL) Immune 120 MeVcm2/mg

- High Impedance LVDS Inputs with Power-Off.

- Accepts Small Swing (330 mV) Differential

Signal Levels

- Low Power Dissipation

- Low Differential Skew

- Low Chip to Chip Skew

- Pin patible with DS26C32A

- patible with IEEE 1596.3 SCI LVDS

Standard

DESCRIPTION

The DS90C032 is a quad CMOS differential line receiver designed for applications requiring ultra low power dissipation and high data rates.

The DS90C032 accepts low voltage differential input signals and translates...