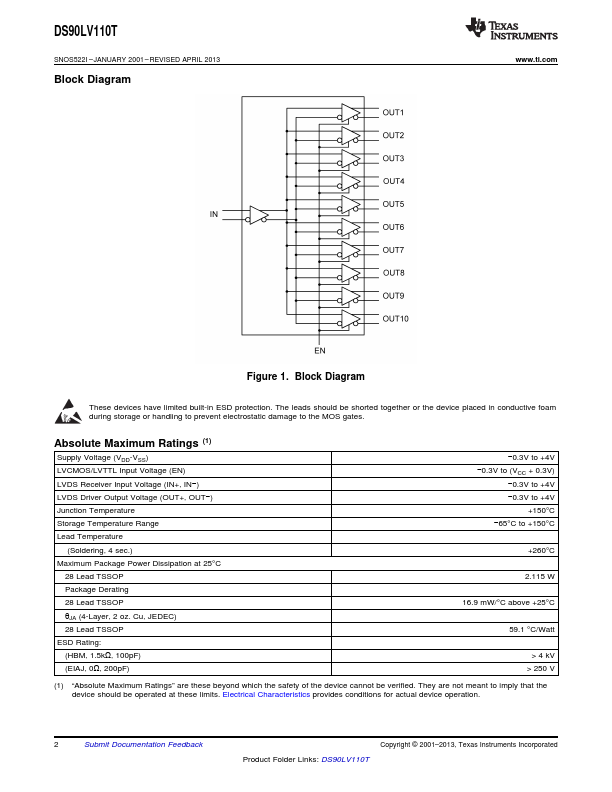

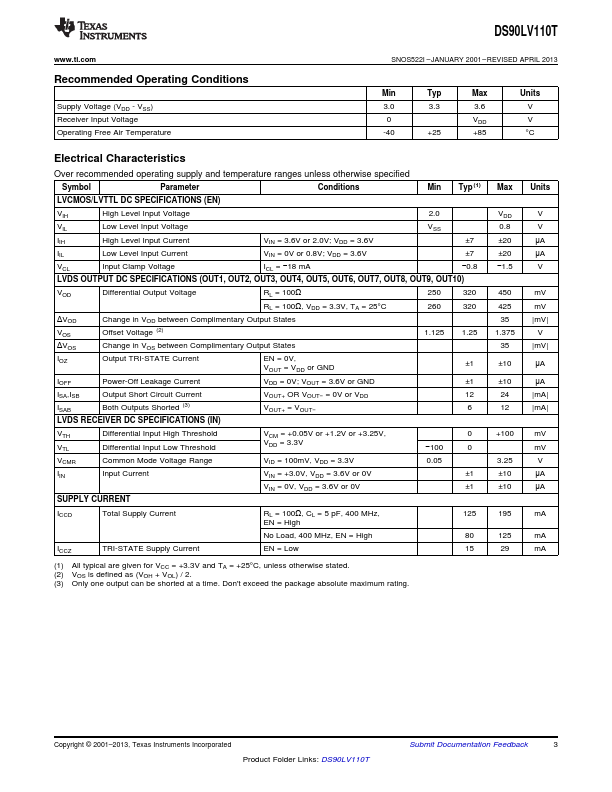

Datasheet Summary

.ti.

SNOS522I

- JANUARY 2001

- REVISED APRIL 2013

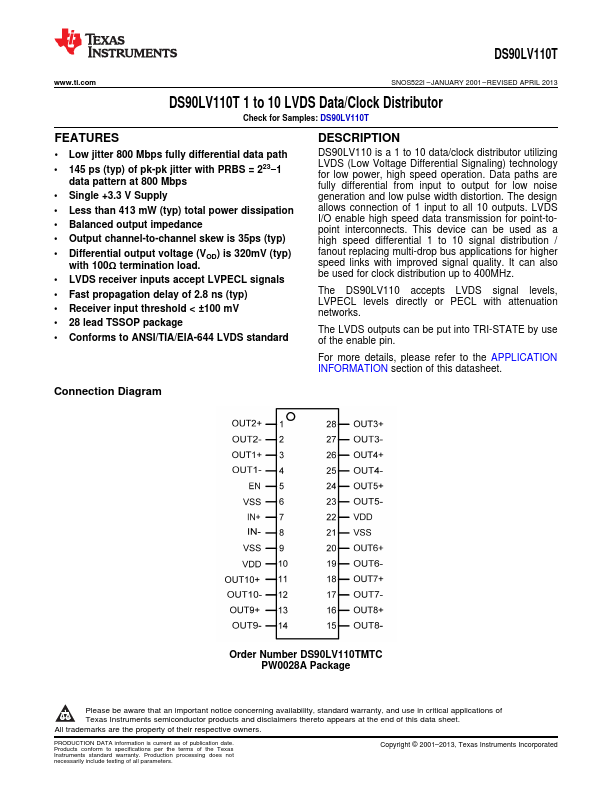

DS90LV110T 1 to 10 LVDS Data/Clock Distributor

Check for Samples: DS90LV110T

Features

- 2 Low jitter 800 Mbps fully differential data path

- 145 ps (typ) of pk-pk jitter with PRBS = 223- 1 data pattern at 800 Mbps

- Single +3.3 V Supply

- Less than 413 mW (typ) total power dissipation

- Balanced output impedance

- Output channel-to-channel skew is 35ps (typ)

- Differential output voltage (VOD) is 320mV (typ) with 100Ω termination load.

- LVDS receiver inputs accept LVPECL signals

- Fast propagation delay of 2.8 ns (typ)

- Receiver input threshold < ±100 mV

- 28 lead TSSOP package

- Conforms to ANSI/TIA/EIA-644 LVDS...