DS90LV110T Overview

Description

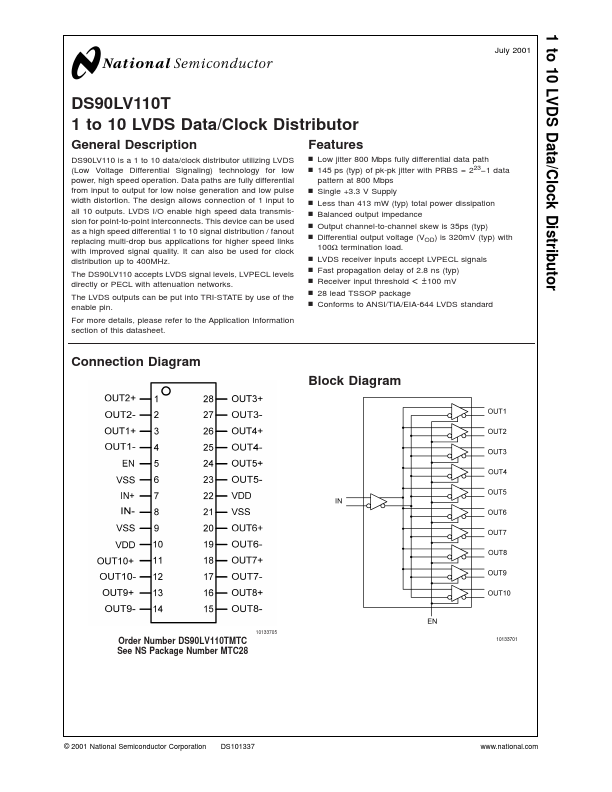

DS90LV110 is a 1 to 10 data/clock distributor utilizing LVDS (Low Voltage Differential Signaling) technology for low power, high speed operation. Data paths are fully differential from input to output for low noise generation and low pulse width distortion.

Key Features

- Single +3.3 V Supply

- Less than 413 mW (typ) total power dissipation

- Balanced output impedance

- Output channel-to-channel skew is 35ps (typ)

- Differential output voltage (VOD) is 320mV (typ) with 100Ω termination load

- LVDS receiver inputs accept LVPECL signals

- Fast propagation delay of 2.8 ns (typ)

- Receiver input threshold < ± 100 mV n 28 lead TSSOP package