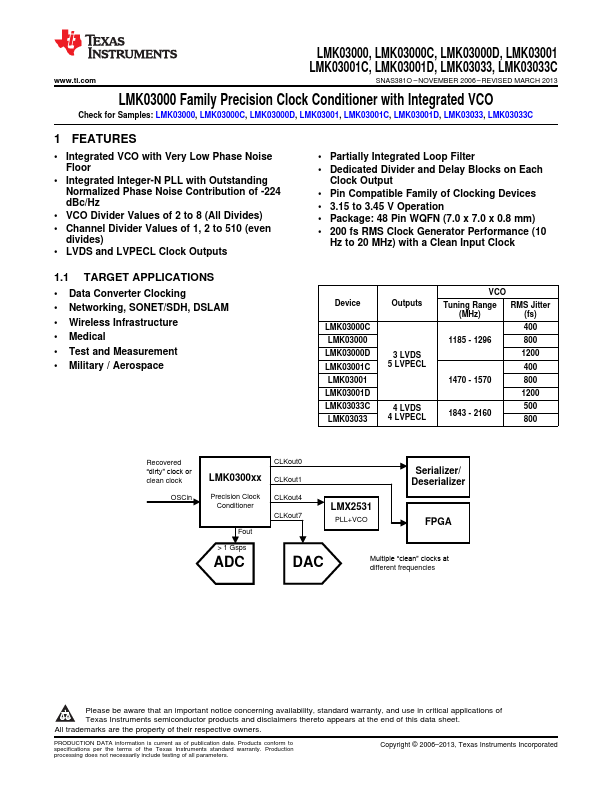

LMK03001C Overview

Key Features

- Integrated VCO with Very Low Phase Noise Floor

- Integrated Integer-N PLL with Outstanding Normalized Phase Noise Contribution of -224 dBc/Hz

- VCO Divider Values of 2 to 8 (All Divides)

- Channel Divider Values of 1, 2 to 510 (even divides)

- LVDS and LVPECL Clock Outputs

- Partially Integrated Loop Filter

- Dedicated Divider and Delay Blocks on Each Clock Output

- Pin Compatible Family of Clocking Devices

- 3.15 to 3.45 V Operation

- Package: 48 Pin WQFN (7.0 x 7.0 x 0.8 mm)