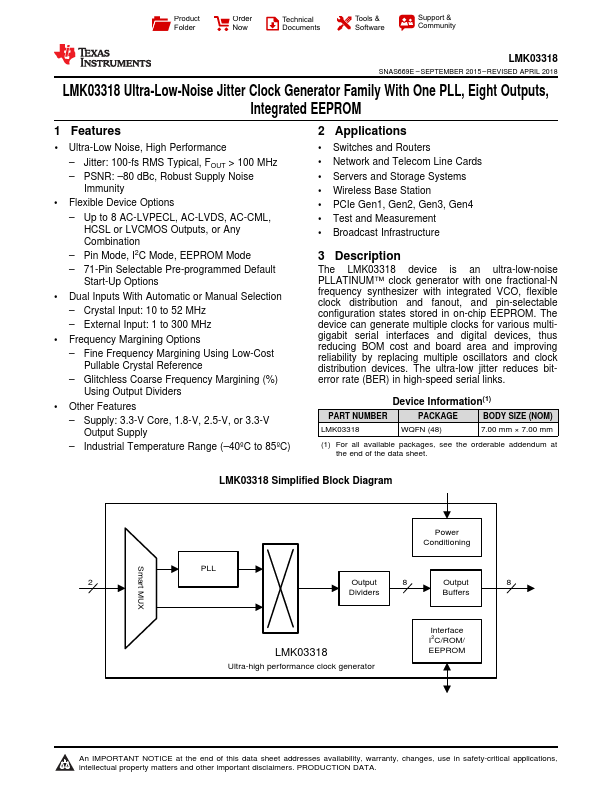

LMK03318 Description

The LMK03318 device is an ultra-low-noise PLLATINUM™ clock generator with one fractional-N frequency synthesizer with integrated VCO, flexible clock distribution and fanout, and pin-selectable configuration states stored in on-chip EEPROM. The device can generate multiple clocks for various multigigabit serial interfaces and digital devices, thus reducing BOM cost and board area and improving reliability by...

LMK03318 Key Features

- 1 Ultra-Low Noise, High Performance

- Jitter: 100-fs RMS Typical, FOUT > 100 MHz

- PSNR: -80 dBc, Robust Supply Noise Immunity

- Flexible Device Options

- Up to 8 AC-LVPECL, AC-LVDS, AC-CML, HCSL or LVCMOS Outputs, or Any bination

- Pin Mode, I2C Mode, EEPROM Mode

- 71-Pin Selectable Pre-programmed Default Start-Up Options

- Dual Inputs With Automatic or Manual Selection

- Crystal Input: 10 to 52 MHz

- External Input: 1 to 300 MHz