LMK03328

LMK03328 is Ultra-Low Jitter Clock Generator manufactured by Texas Instruments.

ures

- 1 Ultra Low Noise, High Performance

- Jitter: 100-fs RMS Typical, FOUT > 100 MHz

- PSNR:

- 80 d Bc, Robust Supply Noise

Immunity

- Flexible Device Options

- Up to 8 AC-LVPECL, AC-LVDS, AC-CML, HCSL or LVCMOS Outputs, or Any bination

- Pin Mode, I2C Mode, and EEPROM Mode

- 71-Pin Selectable Pre-Programmed Default Start-Up Options

- Dual Inputs With Automatic or Manual Selection

- Crystal Input: 10 to 52 MHz

- External Input: 1 to 300 MHz

- Frequency Margining Options

- Fine Frequency Margining (±50 ppm Typical) Using Low-Cost Pullable Crystal Reference

- Glitchless Coarse Frequency Margining (%) Using Output Dividers

- Other Features

- Supply: 3.3-V Core, 1.8-V, 2.5-V, 3.3-V Output Supply

- Industrial Temperature Range (- 40ºC to +85ºC)

- Package: 7-mm × 7-mm 48-WQFN

2 Applications

- Switches and Routers

- Network and Tele Line Cards

- Servers and Storage Systems

- Wireless Base Station

- PCIe Gen1, Gen2, Gen3, Gen4

- Test and Measurement

- Broadcast Infrastructure

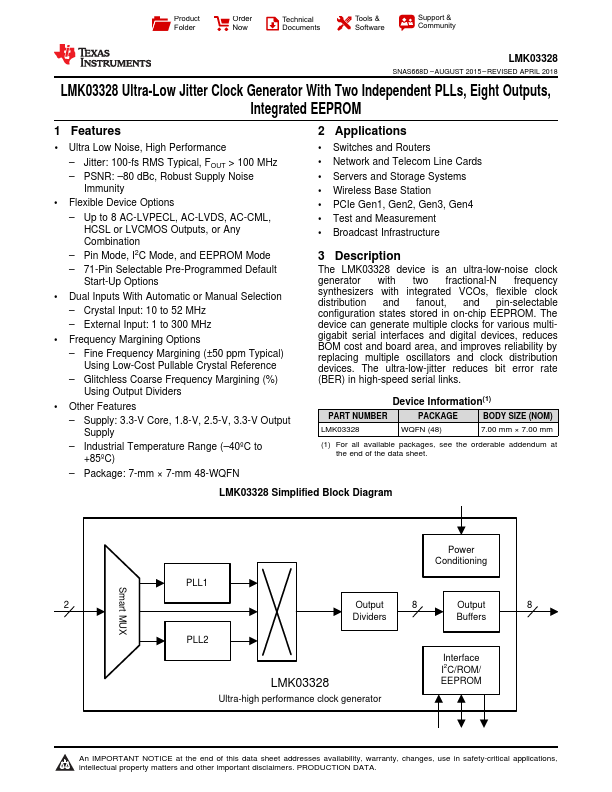

3 Description

The LMK03328 device is an ultra-low-noise clock generator with two fractional-N frequency synthesizers with integrated VCOs, flexible clock distribution and fanout, and pin-selectable configuration states stored in on-chip EEPROM. The device can generate multiple clocks for various multigigabit serial interfaces and digital devices, reduces BOM cost and board area, and improves reliability by replacing multiple oscillators and clock distribution devices. The ultra-low-jitter reduces bit error rate (BER) in high-speed serial...