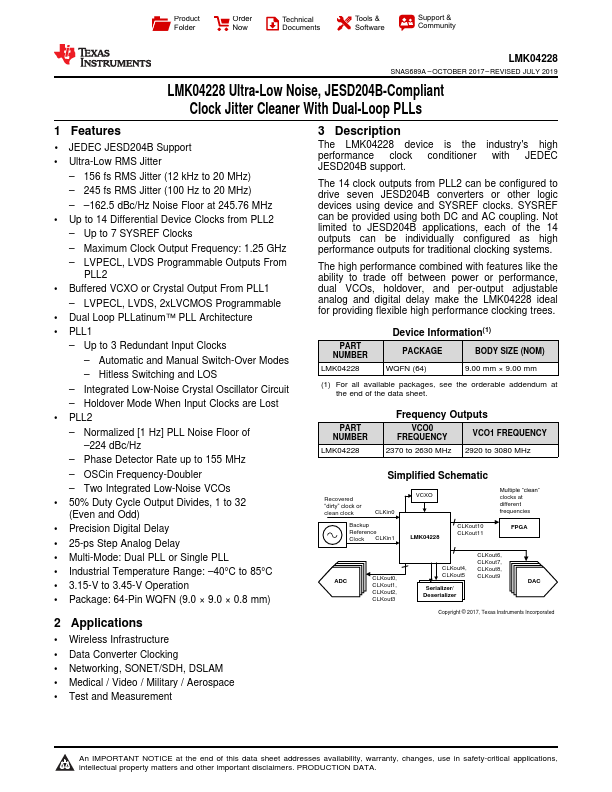

LMK04228 Description

The LMK04228 device is the performance clock conditioner JESD204B support. industry's high with JEDEC The 14 clock outputs from PLL2 can be configured to drive seven JESD204B converters or other logic devices using device and SYSREF clocks. SYSREF can be provided using both DC and AC coupling.

LMK04228 Key Features

- 1 JEDEC JESD204B Support

- Ultra-Low RMS Jitter

- 156 fs RMS Jitter (12 kHz to 20 MHz)

- 245 fs RMS Jitter (100 Hz to 20 MHz)

- 162.5 dBc/Hz Noise Floor at 245.76 MHz

- Up to 14 Differential Device Clocks from PLL2

- Up to 7 SYSREF Clocks

- Maximum Clock Output Frequency: 1.25 GHz

- LVPECL, LVDS Programmable Outputs From

- Buffered VCXO or Crystal Output From PLL1