Datasheet Summary

Product Folder

Order Now

Technical Documents

Tools & Software

Support & munity

SNAS699B

- JANUARY 2017

- REVISED JULY 2019

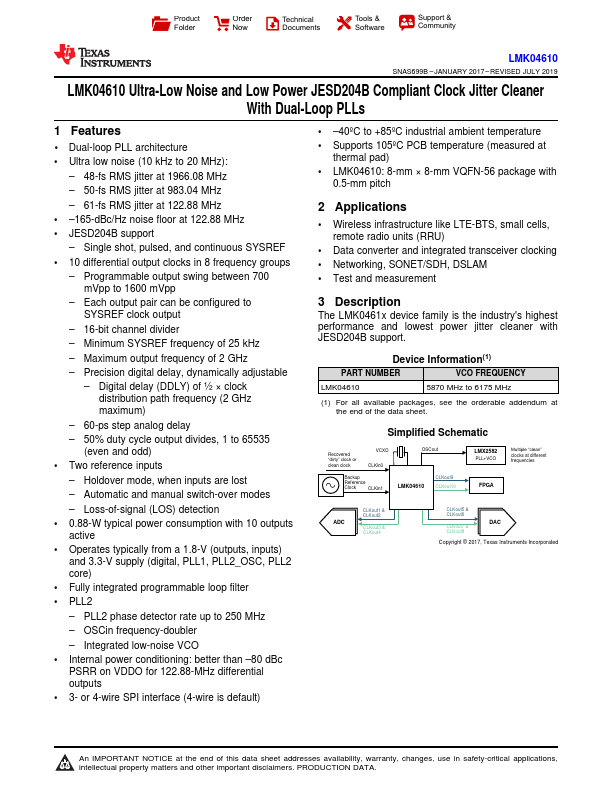

LMK04610 Ultra-Low Noise and Low Power JESD204B pliant Clock Jitter Cleaner With Dual-Loop PLLs

1 Features

- 1 Dual-loop PLL architecture

- Ultra low noise (10 kHz to 20 MHz):

- 48-fs RMS jitter at 1966.08 MHz

- 50-fs RMS jitter at 983.04 MHz

- 61-fs RMS jitter at 122.88 MHz

- - 165-dBc/Hz noise floor at 122.88 MHz

- JESD204B support

- Single shot, pulsed, and continuous SYSREF

- 10 differential output clocks in 8 frequency groups

- Programmable output swing between 700 mVpp to 1600 mVpp

- Each output pair can be configured to

SYSREF clock output

-...