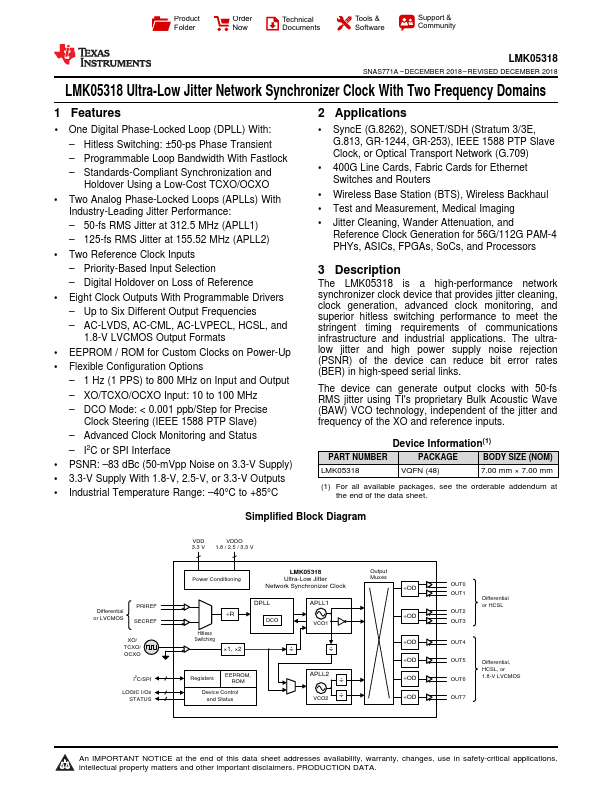

LMK05318 Description

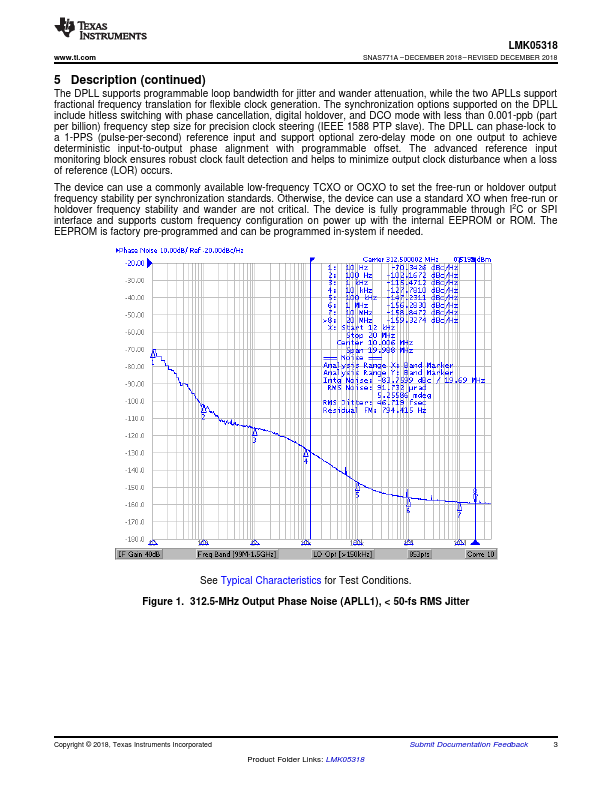

The LMK05318 is a high-performance network synchronizer clock device that provides jitter cleaning, clock generation, advanced clock monitoring, and superior hitless switching performance to meet the stringent timing requirements of munications infrastructure and industrial applications. The ultralow jitter and high power supply noise rejection (PSNR) of the device can reduce bit error rates (BER) in high-speed...

LMK05318 Key Features

- Hitless Switching: ±50-ps Phase Transient

- Programmable Loop Bandwidth With Fastlock

- Standards-pliant Synchronization and Holdover Using a Low-Cost TCXO/OCXO

- Two Analog Phase-Locked Loops (APLLs) With Industry-Leading Jitter Performance

- 50-fs RMS Jitter at 312.5 MHz (APLL1)

- 125-fs RMS Jitter at 155.52 MHz (APLL2)

- Two Reference Clock Inputs

- Priority-Based Input Selection

- Digital Holdover on Loss of Reference

- Eight Clock Outputs With Programmable Drivers