SM320C6201 Overview

Key Specifications

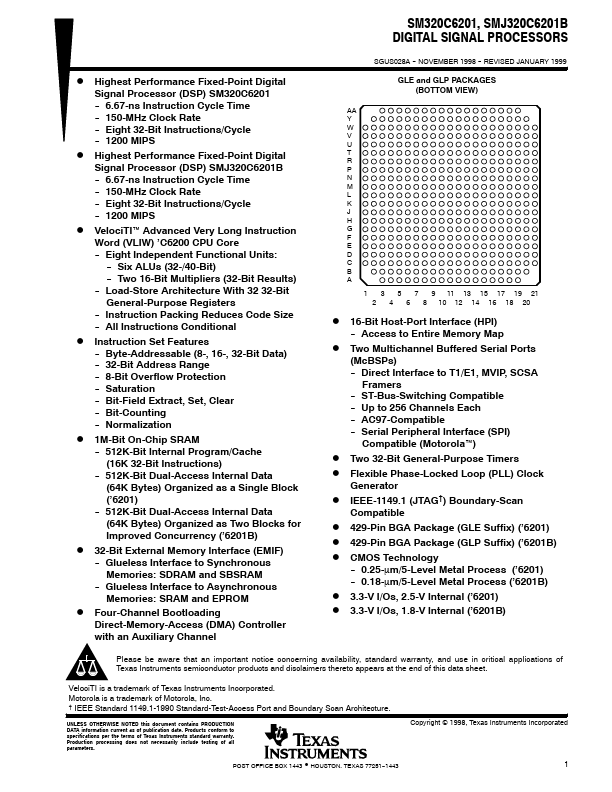

Package: FCBGA

Mount Type: Surface Mount

Pins: 352

Operating Voltage: 2.5 V

Key Features

- 512K-Bit Internal Program/Cache (16K 32-Bit Instructions)

- 512K-Bit Dual-Access Internal Data (64K Bytes) Organized as a Single Block (’6201)

- Glueless Interface to Synchronous Memories: SDRAM and SBSRAM