SN10KHT5574

SN10KHT5574 is Octal ECL-to-TTL Translator manufactured by Texas Instruments.

description

6Q 10 7Q 11

15 6D 14 7D

This octal ECL-to-TTL translator is designed to

8Q 12 13 8D provide efficient translation between a 10KH ECL signal environment and a TTL signal environment.

This device is designed specifically to improve the performance and density of ECL-to-TTL CPU/bus-oriented functions such as memory-address drivers, clock drivers, and bus-oriented receivers and transmitters.

The eight flip-flops of the SN10KHT5574 are edge-triggered D-type flip-flops. On the positive transition of the clock, the Q outputs are set to the logic levels that were set up at the D inputs.

A buffered output-enable input (OE) can be used to place the eight outputs in either a normal logic state (high or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance third state and increased drive provide the capability to drive bus lines without need for interface or pullup ponents.

The output-enable input OE does not affect the internal operations of the flip-flops. Old data can be retained or new data can be entered while the outputs are off.

The SN10KHT5574 is characterized for operation from 0°C to 75°C.

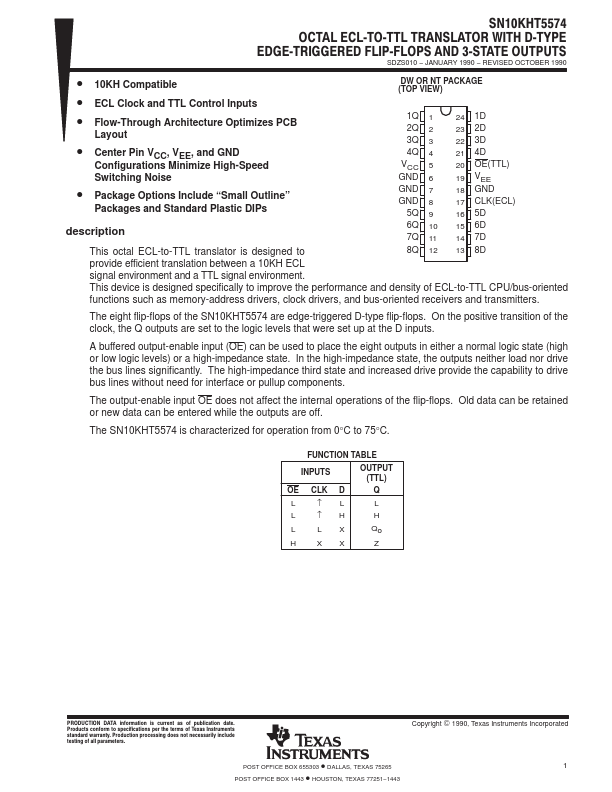

FUNCTION TABLE

INPUTS

OUTPUT (TTL)

OE CLK D

L ↑L

L ↑H

L LX

Qo

H XX

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1990, Texas Instruments Incorporated

- POST OFFICE BOX 655303 DALLAS, TEXAS 75265

- POST OFFICE BOX 1443 HOUSTON, TEXAS 77251- 1443

SN10KHT5574 OCTAL ECLĆTOĆTTL TRANSLATOR WITH DĆTYPE EDGEĆTRIGGERED FLIPĆFLOPS AND 3ĆSTATE OUTPUTS

SDZS010

- JANUARY 1990

- REVISED OCTOBER 1990 logic symbol† logic diagram (positive logic)

17 CLK

20 OE

ECL/TTL C1 EN

OE CLK

20 17

ECL/TTL

1D 24...