Datasheet Summary

D State-of-the-Art EPIC-ΙΙB™ BiCMOS Design

Significantly Reduces Power Dissipation

D ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

D Latch-Up Performance Exceeds 500 mA Per

JEDEC Standard JESD-17

D Typical VOLP (Output Ground Bounce) < 1 V at VCC = 5 V, TA = 25°C

D High-Impedance State During Power Up and Power Down

D Designed to Facilitate Incident-Wave

Switching for Line Impedances of 25 Ω or Greater

D Distributed VCC and GND Pin Configuration

Minimizes High-Speed Switching Noise

D Bus Hold on Data Inputs Eliminates the

Need for External Pullup/Pulldown Resistors

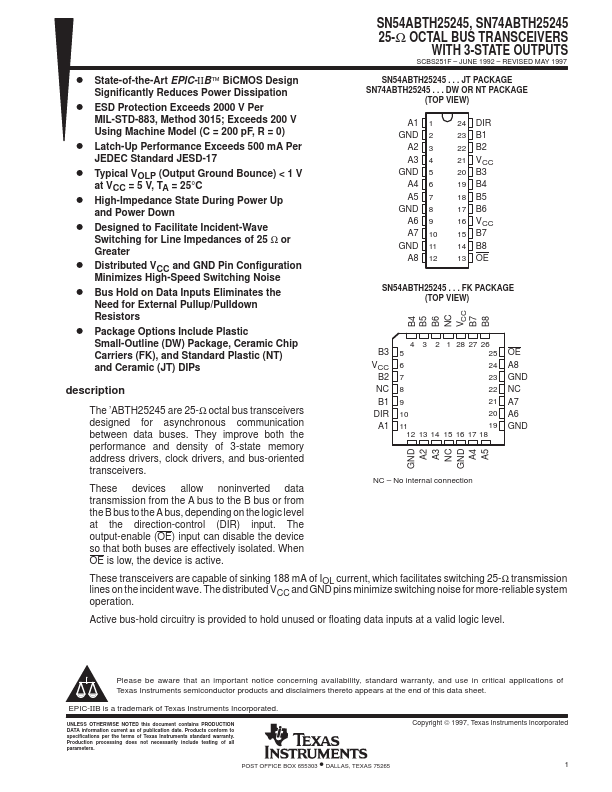

D Package Options Include Plastic

Small-Outline (DW)...