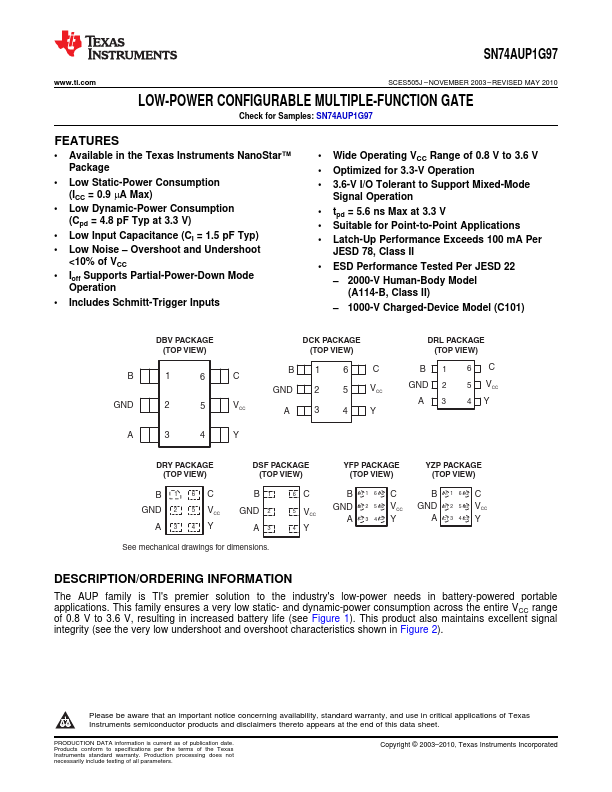

SN74AUP1G97 Overview

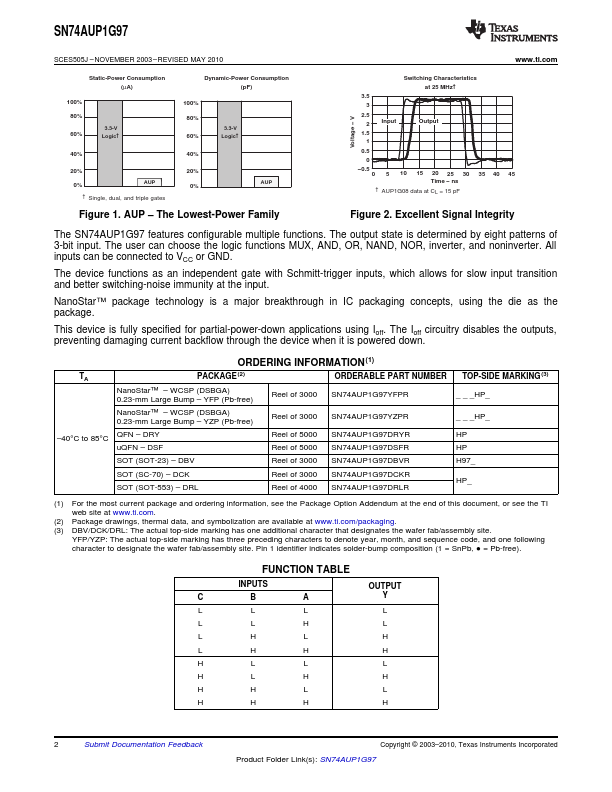

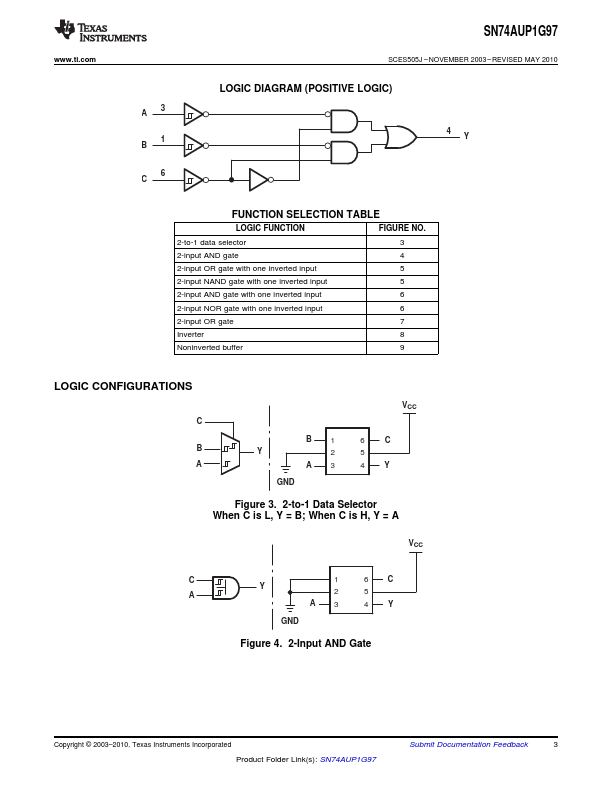

/ORDERING INFORMATION The AUP family is TI's premier solution to the industry's low-power needs in battery-powered portable applications. This family ensures a very low static- and dynamic-power consumption across the entire VCC range of 0.8 V to 3.6 V, resulting in increased battery life (see Figure 1). This product also maintains excellent signal integrity (see the very low undershoot and overshoot characteristics...

SN74AUP1G97 Key Features

- Available in the Texas Instruments NanoStar™ Package

- Low Static-Power Consumption (ICC = 0.9 mA Max)

- Low Dynamic-Power Consumption (Cpd = 4.8 pF Typ at 3.3 V)

- Low Input Capacitance (CI = 1.5 pF Typ)

- Low Noise

- Overshoot and Undershoot

- Ioff Supports Partial-Power-Down Mode

- Includes Schmitt-Trigger Inputs

- Wide Operating VCC Range of 0.8 V to 3.6 V

- Optimized for 3.3-V Operation

SN74AUP1G97 Applications

- Latch-Up Performance Exceeds 100 mA Per

- ESD Performance Tested Per JESD 22