SN74AUP1G00 Overview

Description

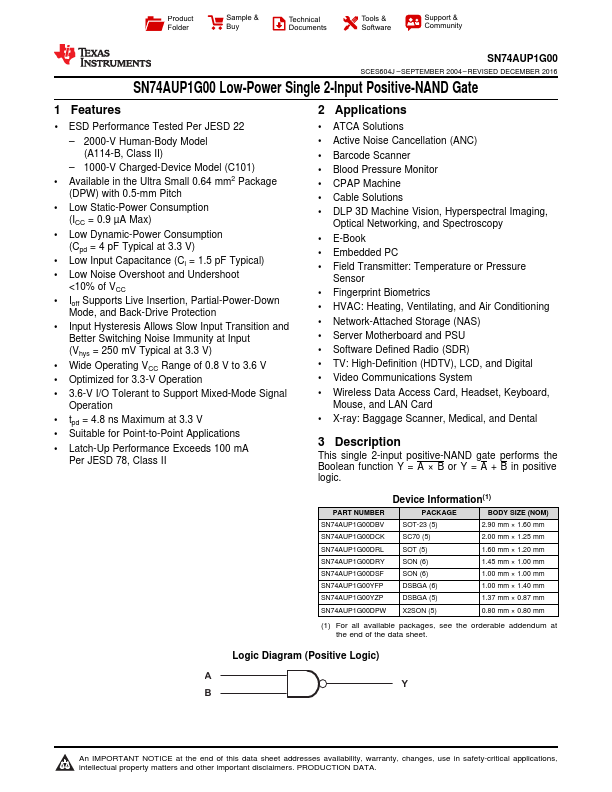

This single 2-input positive-NAND gate performs the Boolean function Y = A × B or Y = A + B in positive logic. Device Information(1) PART NUMBER.

Key Features

- 1 ESD Performance Tested Per JESD 22 – 2000-V Human-Body Model (A114-B, Class II) – 1000-V Charged-Device Model (C101)

- Available in the Ultra Small 0.64 mm2 Package (DPW) with 0.5-mm Pitch

- Low Static-Power Consumption (ICC = 0.9 µA Max)

- Low Dynamic-Power Consumption (Cpd = 4 pF Typical at 3.3 V)

- Low Input Capacitance (Ci = 1.5 pF Typical)

- Low Noise Overshoot and Undershoot <10% of VCC

- Ioff Supports Live Insertion, Partial-Power-Down Mode, and Back-Drive Protection

- Input Hysteresis Allows Slow Input Transition and Better Switching Noise Immunity at Input (Vhys = 250 mV Typical at 3.3 V)

- Wide Operating VCC Range of 0.8 V to 3.6 V

- Optimized for 3.3-V Operation