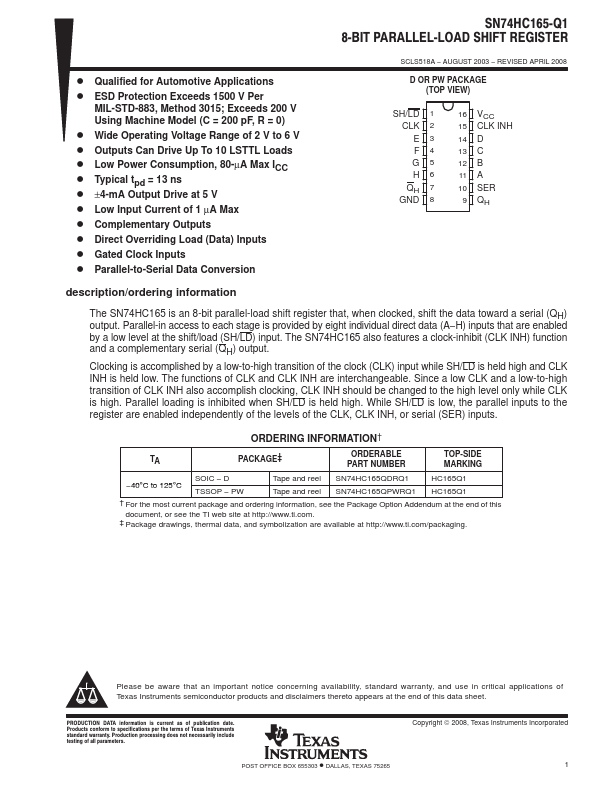

SN74HC165-Q1

Key Features

- a clock-inhibit (CLK INH) function and a plementary serial (QH) output

- Clocking is acplished by a low-to-high transition of the clock (CLK) input while SH/LD is held high and CLK INH is held low

- The functions of CLK and CLK INH are interchangeable

- Parallel loading is inhibited when SH/LD is held high

- While SH/LD is low, the parallel inputs to the register are enabled independently of the levels of the CLK, CLK INH, or serial (SER) inputs