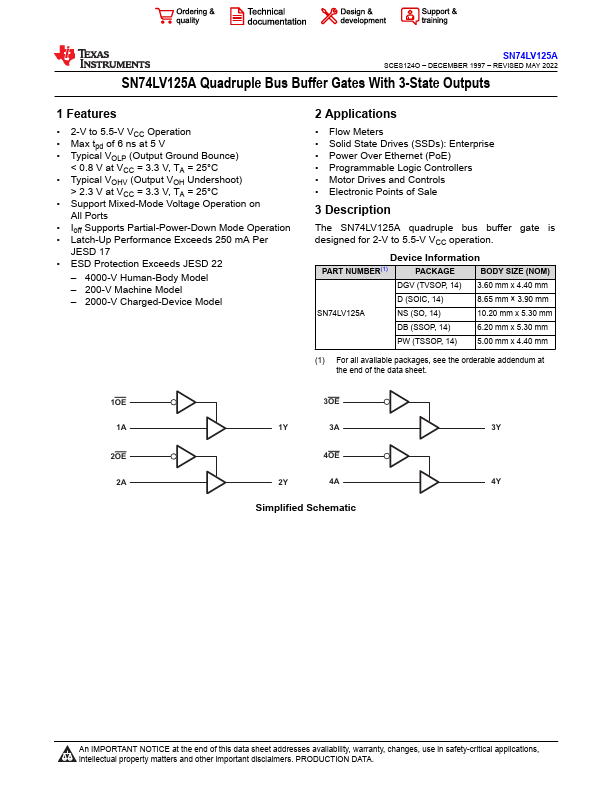

SN74LV125A Description

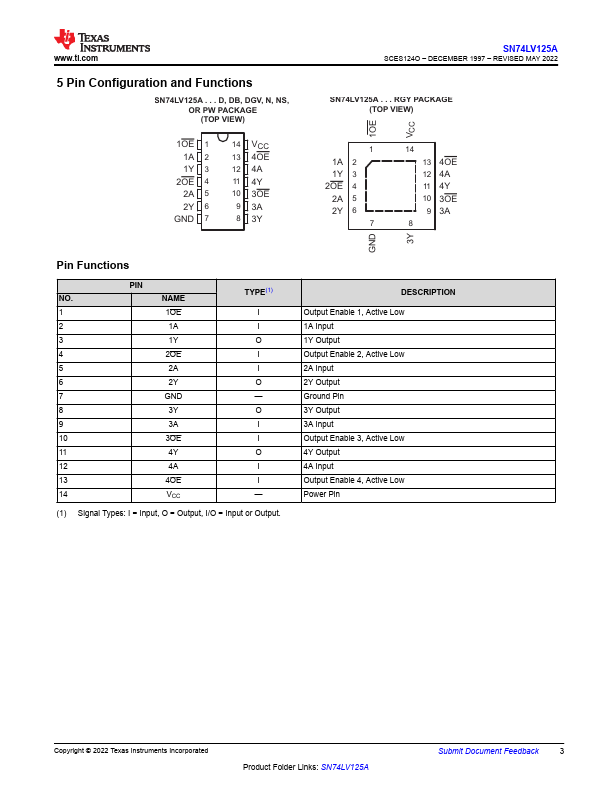

The SN74LV125A quadruple bus buffer gate is designed for 2-V to 5.5-V VCC operation. SN74LV125A SCES124O DECEMBER 1997 REVISED MAY 2022 .ti.

SN74LV125A Key Features

- 2-V to 5.5-V VCC Operation

- Max tpd of 6 ns at 5 V

- Typical VOLP (Output Ground Bounce)

- Typical VOHV (Output VOH Undershoot)

- Support Mixed-Mode Voltage Operation on

- Ioff Supports Partial-Power-Down Mode Operation

- ESD Protection Exceeds JESD 22

- 4000-V Human-Body Model

- 200-V Machine Model

- 2000-V Charged-Device Model