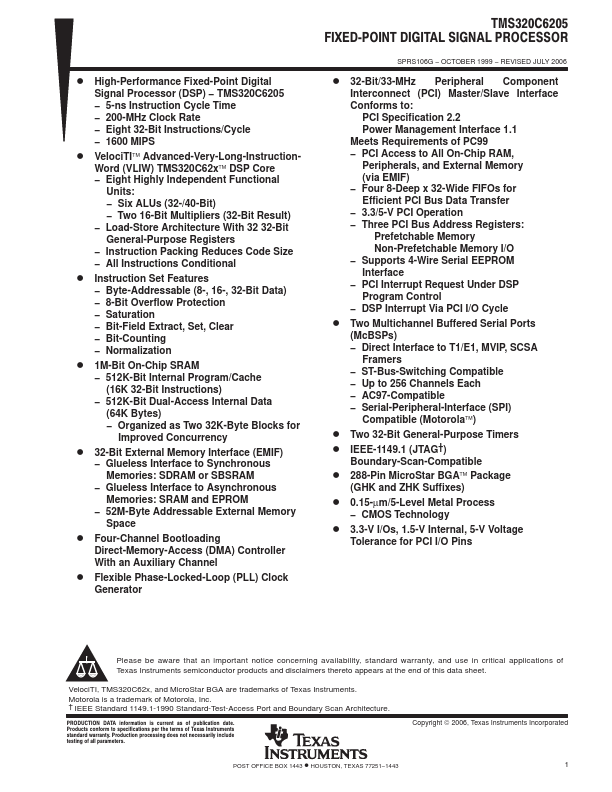

TMS320C6205

Key Features

- 8-Bit Overflow Protection

- Normalization D 1M-Bit On-Chip SRAM

- 512K-Bit Dual-Access Internal Data (64K Bytes)

- Organized as Two 32K-Byte Blocks for Improved Concurrency D 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Synchronous Memories: SDRAM or SBSRAM

- Glueless Interface to Asynchronous Memories: SRAM and EPROM

- Four 8-Deep x 32-Wide FIFOs for Efficient PCI Bus Data Transfer

- 3.3/5-V PCI Operation

- Three PCI Bus Address Registers: Prefetchable Memory Non-Prefetchable Memory I/O

- Supports 4-Wire Serial EEPROM Interface