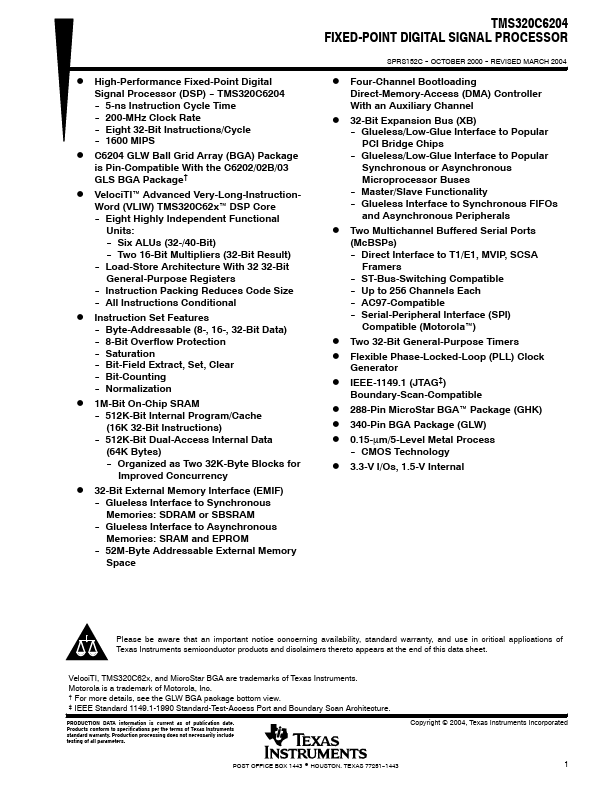

TMS320C6204

TMS320C6204 is FIXED-POINT DIGITAL SIGNAL PROCESSOR manufactured by Texas Instruments.

Features

-- Byte-Addressable (8-, 16-, 32-Bit Data) -- 8-Bit Overflow Protection -- Saturation -- Bit-Field Extract, Set, Clear -- Bit-Counting -- Normalization

D 1M-Bit On-Chip SRAM

-- 512K-Bit Internal Program/Cache (16K 32-Bit Instructions)

-- 512K-Bit Dual-Access Internal Data (64K Bytes) -- Organized as Two 32K-Byte Blocks for Improved Concurrency

D 32-Bit External Memory Interface (EMIF)

-- Glueless Interface to Synchronous Memories: SDRAM or SBSRAM

-- Glueless Interface to Asynchronous Memories: SRAM and EPROM

-- 52M-Byte Addressable External Memory Space

TMS320C6204 FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS152C -- OCTOBER 2000 -- REVISED MARCH 2004

D Four-Channel Bootloading

Direct-Memory-Access (DMA) Controller With an Auxiliary Channel

D 32-Bit Expansion Bus (XB)

-- Glueless/Low-Glue Interface to Popular PCI Bridge Chips

-- Glueless/Low-Glue Interface to Popular Synchronous or Asynchronous Microprocessor Buses

-- Master/Slave Functionality -- Glueless Interface to Synchronous FIFOs and Asynchronous Peripherals

D Two Multichannel Buffered Serial Ports

(Mc BSPs) -- Direct Interface to T1/E1, MVIP, SCSA

Framers -- ST-Bus-Switching patible -- Up to 256 Channels Each -- AC97-patible -- Serial-Peripheral Interface (SPI) patible (Motorola™)

D Two 32-Bit General-Purpose Timers D Flexible Phase-Locked-Loop (PLL) Clock

Generator

D IEEE-1149.1 (JTAG‡)

Boundary-Scan-patible

D 288-Pin Micro Star BGA™ Package (GHK) D 340-Pin BGA Package (GLW) D 0.15-μm/5-Level Metal Process

-- CMOS Technology

D 3.3-V I/Os, 1.5-V Internal

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Veloci TI, TMS320C62x, and Micro Star BGA are trademarks of Texas Instruments.

Motorola is a trademark of Motorola, Inc. † For more details, see the GLW BGA package bottom view. ‡ IEEE Standard 1149.1-1990 Standard-Test-Access Port...