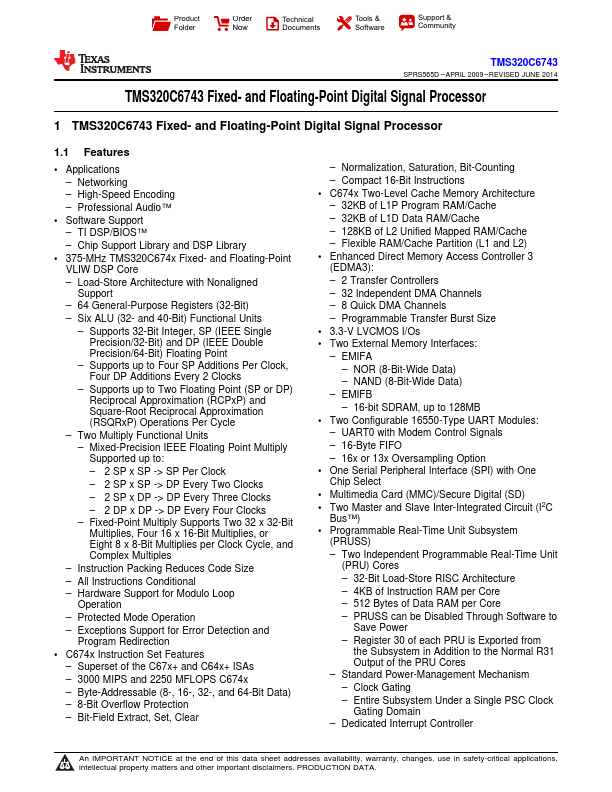

TMS320C6743

TMS320C6743 is Fixed- and Floating-Point DSP manufactured by Texas Instruments.

Features

- Applications

- Networking

- High-Speed Encoding

- Professional Audio™

- Software Support

- TI DSP/BIOS™

- Chip Support Library and DSP Library

- 375-MHz TMS320C674x Fixed- and Floating-Point VLIW DSP Core

- Load-Store Architecture with Nonaligned Support

- 64 General-Purpose Registers (32-Bit)

- Six ALU (32- and 40-Bit) Functional Units

- Supports 32-Bit Integer, SP (IEEE Single Precision/32-Bit) and DP (IEEE Double Precision/64-Bit) Floating Point

- Supports up to Four SP Additions Per Clock, Four DP Additions Every 2 Clocks

- Supports up to Two Floating Point (SP or DP) Reciprocal Approximation (RCPx P) and Square-Root Reciprocal Approximation (RSQRx P) Operations Per Cycle

- Two Multiply Functional Units

- Mixed-Precision IEEE Floating Point Multiply Supported up to:

- 2 SP x SP -> SP Per Clock

- 2 SP x SP -> DP Every Two Clocks

- 2 SP x DP -> DP Every Three Clocks

- 2 DP x DP -> DP Every Four Clocks

- Fixed-Point Multiply Supports Two 32 x 32-Bit Multiplies, Four 16 x 16-Bit Multiplies, or Eight 8 x 8-Bit Multiplies per Clock Cycle, and plex Multiples

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Hardware Support for Modulo Loop Operation

- Protected Mode Operation

- Exceptions Support for Error Detection and Program Redirection

- C674x Instruction Set Features

- Superset of the C67x+ and C64x+ ISAs

- 3000 MIPS and 2250 MFLOPS C674x

- Byte-Addressable (8-, 16-, 32-, and 64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- Normalization, Saturation, Bit-Counting

- pact 16-Bit Instructions

- C674x Two-Level Cache Memory Architecture

- 32KB of L1P Program RAM/Cache

- 32KB of L1D Data...