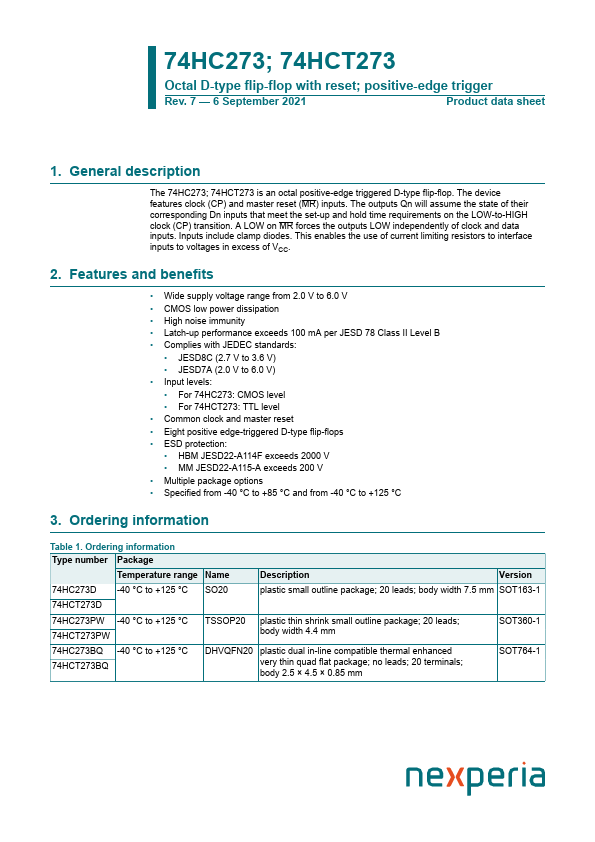

74HC273D Overview

Key Specifications

Package: SOP

Pins: 20

Operating Voltage: 5 V

Max Voltage (typical range): 6 V

Description

The 74HC273; 74HCT273 is an octal positive-edge triggered D-type flip-flop. The device features clock (CP) and master reset (MR) inputs.

Key Features

- Wide supply voltage range from 2.0 V to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- Complies with JEDEC standards