Description

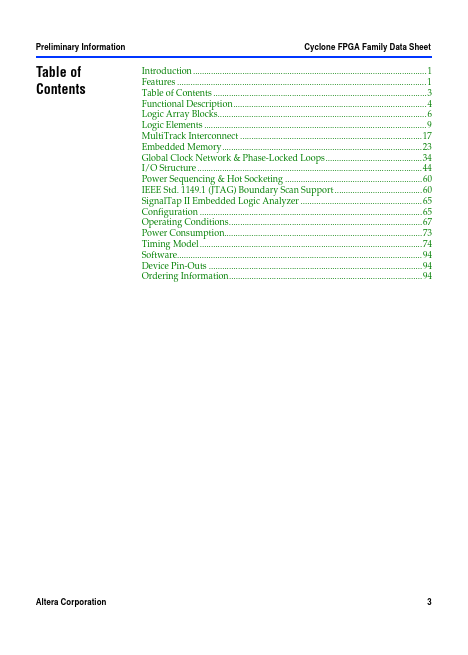

Logic Array Blocks6 Logic Elements 9 MultiTrack Interconnect 17 Embedded Memory23 Global Clock Network & Phase-Locked Loops34 I/O Structure 44 Power Sequencing & Hot Socketing 60 IEEE Std.

Features

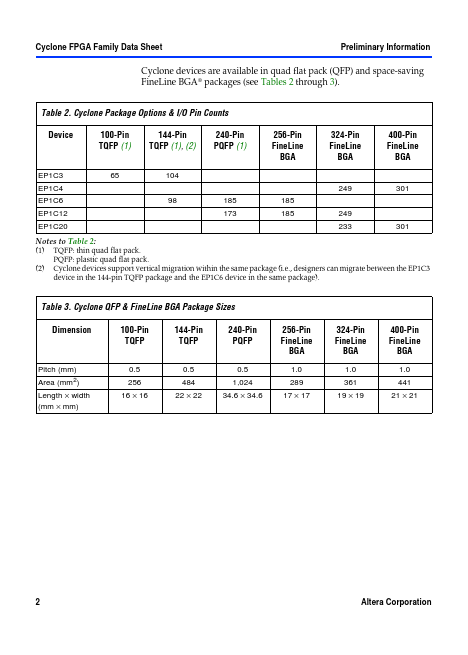

- The CycloneTM field programmable gate array family is based on a 1.5-V, 0.13-µm, all-layer copper SRAM process, with densities up to 20,060 logic elements (LEs) and up to 288 Kbits of RAM. With features like phaselocked loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements, Cyclone devices are a cost-effective solution for data-path.