AD9865

FEATURES

Low cost 3.3 V CMOS Mx FETM for broadband modems 10-bit D/A converter

2×/4× interpolation filter 200 MSPS DAC update rate Integrated 23 d Bm line driver with 19.5 d B gain control 10-bit, 80 MSPS A/D converter

- 12 d B to +48 d B low noise Rx PGA (< 3.0 n V/rt Hz) Third order, programmable low-pass filter Flexible digital data path interface Half- and full-duplex operation Backward-patible with AD9975 and AD9875 Various power-down/reduction modes Internal clock multiplier (PLL) 2 auxiliary programmable clock outputs Available in 64-lead chip scale package or bare die

APPLICATIONS

Powerline networking VDSL and HPNA

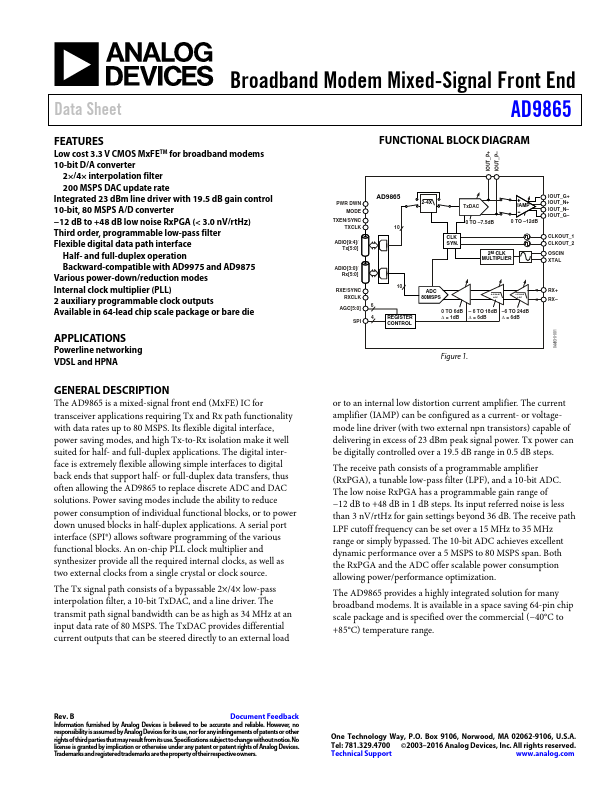

FUNCTIONAL BLOCK DIAGRAM

IOUT_P+ IOUT_P-

PWR DWN MODE

TXEN/SYNC TXCLK

ADIO[9:4]/ Tx[5:0]

ADIO[3:0]/ Rx[5:0]

RXE/SYNC RXCLK

AGC[5:0]

2-4X

Tx DAC

IAMP

0 TO

- 7.5d B

0 TO

- 12d B

CLK SYN.

2M CLK MULTIPLIER

10 ADC

80MSPS

2-POLE LPF

1-POLE LPF

4 REGISTER CONTROL

0 TO 6d B

- 6 TO...