Datasheet Details

- Part number

- ADSP-21561, ADSP-21560

- Manufacturer

- Analog Devices ↗

- File Size

- 2.57 MB

- Datasheet

- ADSP-21560-AnalogDevices.pdf

- Description

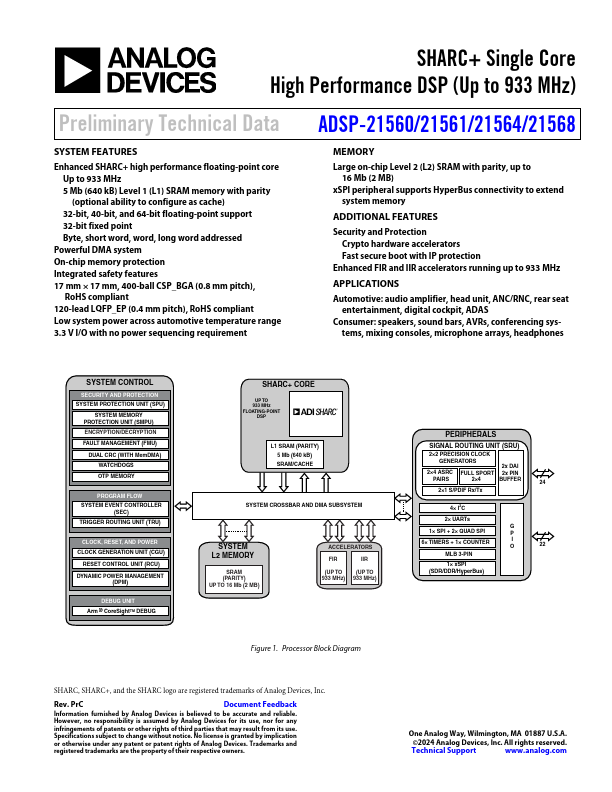

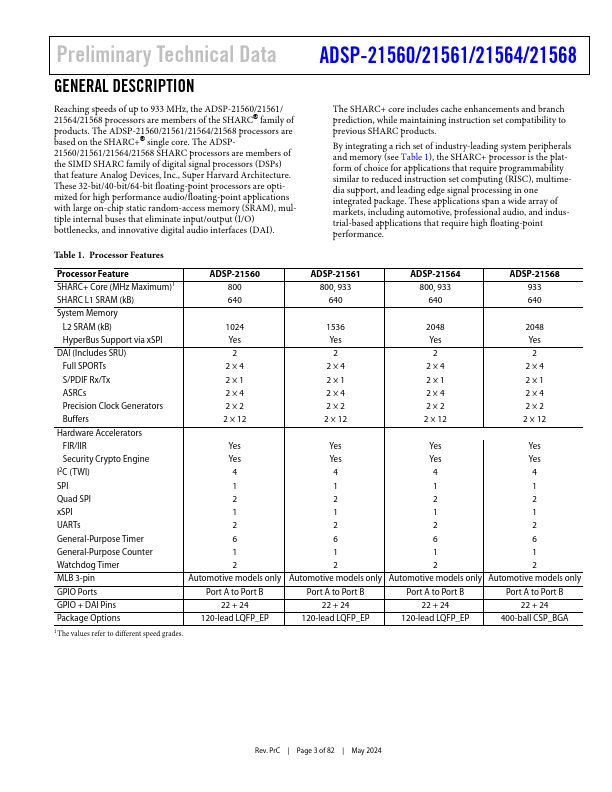

- SHARC+ Single Core High Performance DSP

- Note

- This datasheet PDF includes multiple part numbers: ADSP-21561, ADSP-21560.

Please refer to the document for exact specifications by model.