Description

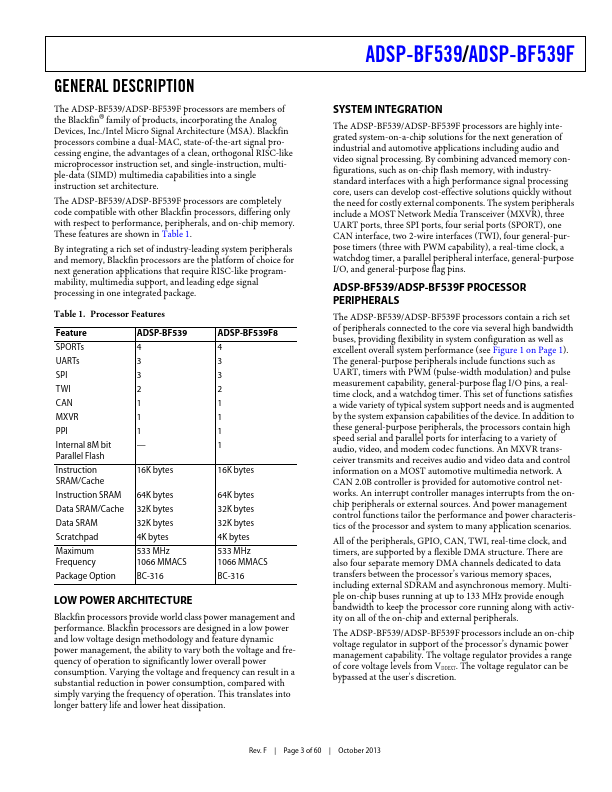

4 Low Power Architecture 4 System Integration 4 ADSP-BF539/ADSP-BF539F Processor Peripherals 4 Blackfin Processor Core 5 Memory Architecture 5 DMA Controllers 10 Real Time Clock 10 Watchdog Timer 11 Timers 11 Serial Ports (SPORTs) 11 Serial Peripheral Interface (SPI) Ports 11 Two Wire Interface 12 UART Port 12 Programmable I/O Pins 12 Parallel Peripheral Interface 13 Controller Area Network (CAN) Interface 14 Media Transceiver MAC layer (MXVR) 14 Dynamic Power Management 15 Vo

Features

- Preliminary Technical Data

1.0 V to 1.2 V core VDD with on-chip voltage regulation 3.3 V tolerant I/O with specific 5 V tolerant pins 316-ball Pb-free mini-BGA package Up to 500 MHz high performance Blackfin processor Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifter RISC-like register and instruction model for ease of programming and compiler friendly support Advanced debug, trace, and performance monitoring

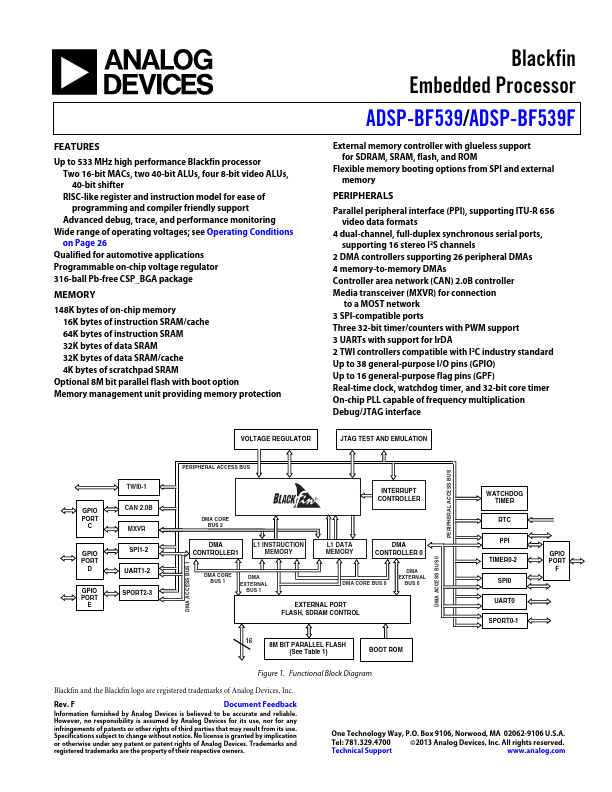

Blackfin® Embedded Processor ADSP-BF539/ADSP-BF539F

External me.