Description

3

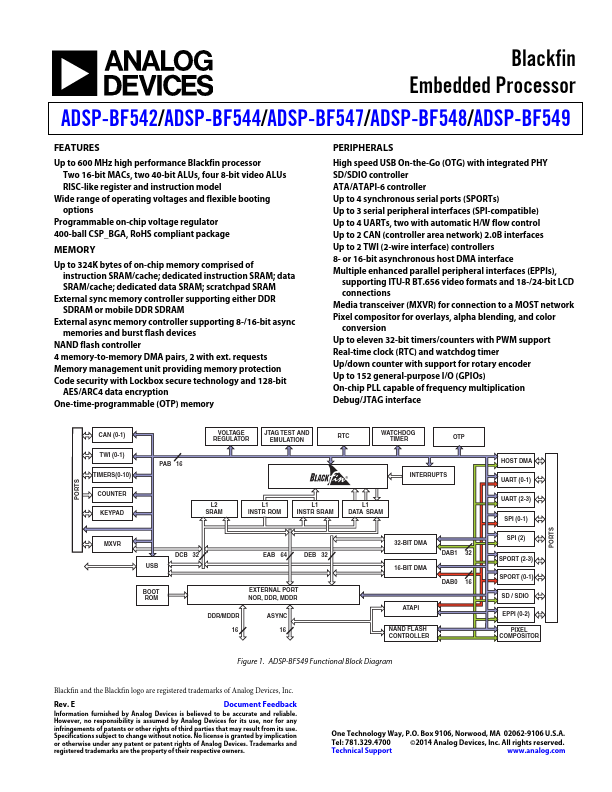

Low Power Architecture 4 System Integration 4 Blackfin Processor Peripherals 4 Blackfin Processor Core 4 Memory Architecture 6 DMA Controllers 9 Real-Time Clock 10 Watchdog Timer 10 Timers 10 Up/Down Counter and Thumbwheel Interface 11 Serial Ports (SPORTs) 11 Serial Peripheral Interface (SPI) Ports 11 UART Ports (UARTs) 11 Controller Area Network (CAN) 12 TWI Controller Interface 12 Ports 12 Pixel Compositor (PIXC) 13 Enhanced Parallel Peripheral Interface (EPPI) 13 USB On-

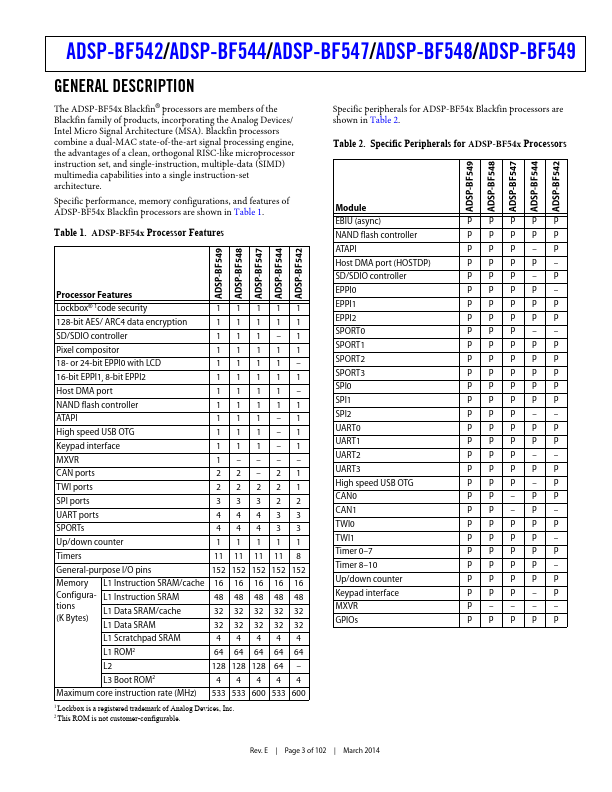

Features

- Up to 600 MHz high performance Blackfin processor Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs RISC-like register and instruction model

Wide range of operating voltages and flexible booting options

Programmable on-chip voltage regulator 400-ball CSP_BGA, RoHS compliant package

MEMORY

Up to 324K bytes of on-chip memory comprised of instruction SRAM/cache; dedicated instruction SRAM; data SRAM/cache; dedicated data SRAM; scratchpad SRAM

External sync memory controller supporting either.