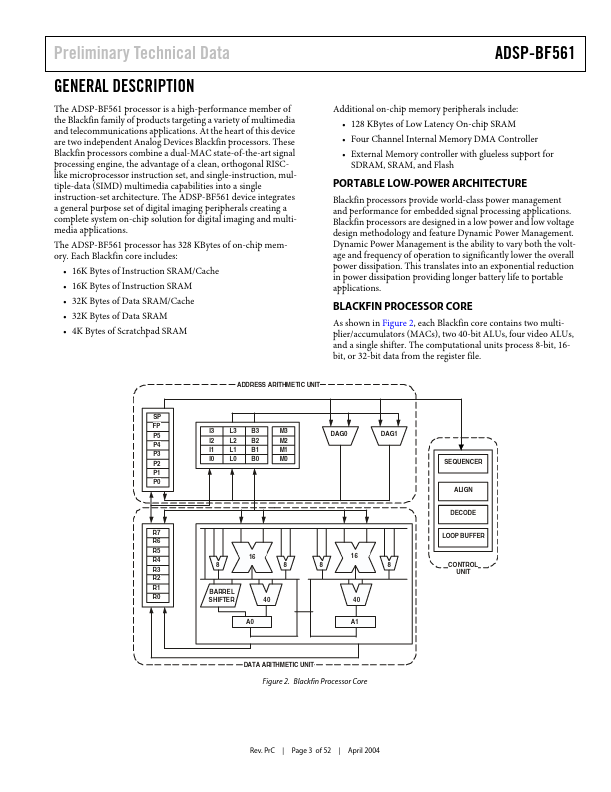

Description

3 Portable Low-Power Architecture 3 Blackfin Processor Core 3 Memory Architecture 4 Internal (On-chip) Memory 4 External (Off-Chip) Memory 5 I/O Memory Space 6 Booting 6 Event Handling 6 Core Event Controller (CEC) 6 System Interrupt Controller (SIC) 6 Event Control 7 DMA Controllers 8 WatchDog Timers 8 Serial Ports (SPORTs) 9 Serial Peripheral Interface (SPI) Ports 9 UART Port 9 Programmable Flags (PFx) 10 Timers 10 Parallel Peripheral Interface 10 General Purpose Mode Descr

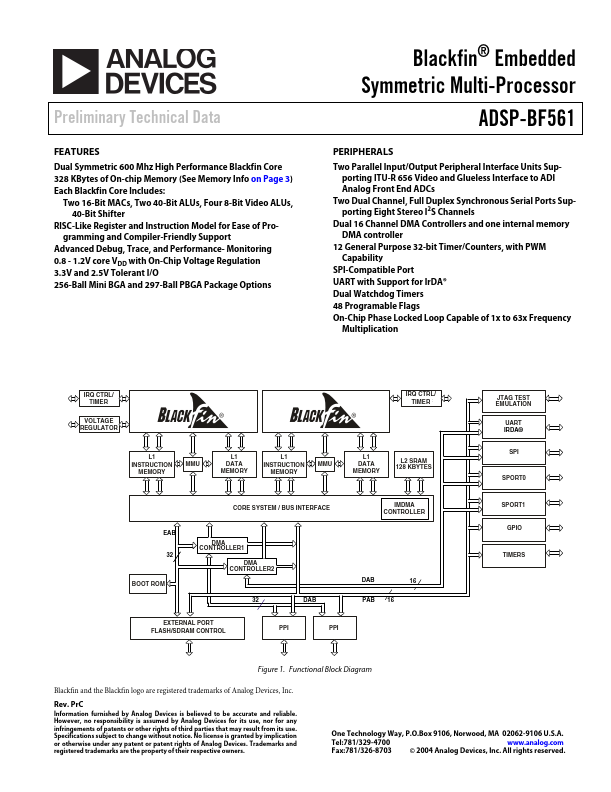

Features

- Preliminary Technical Data

Dual Symmetric 600 Mhz High Performance Blackfin Core 328 KBytes of On-chip Memory (See Memory Info on Page 3) Each Blackfin Core Includes: Two 16-Bit MACs, Two 40-Bit ALUs, Four 8-Bit Video ALUs, 40-Bit Shifter RISC-Like Register and Instruction Model for Ease of Programming and Compiler-Friendly Support Advanced Debug, Trace, and Performance- Monitoring 0.8 - 1.2V core VDD with On-Chip Voltage Regulation 3.3V and 2.5V Tolerant I/O 256-Ball Mini BGA and 297-Ball PBGA.