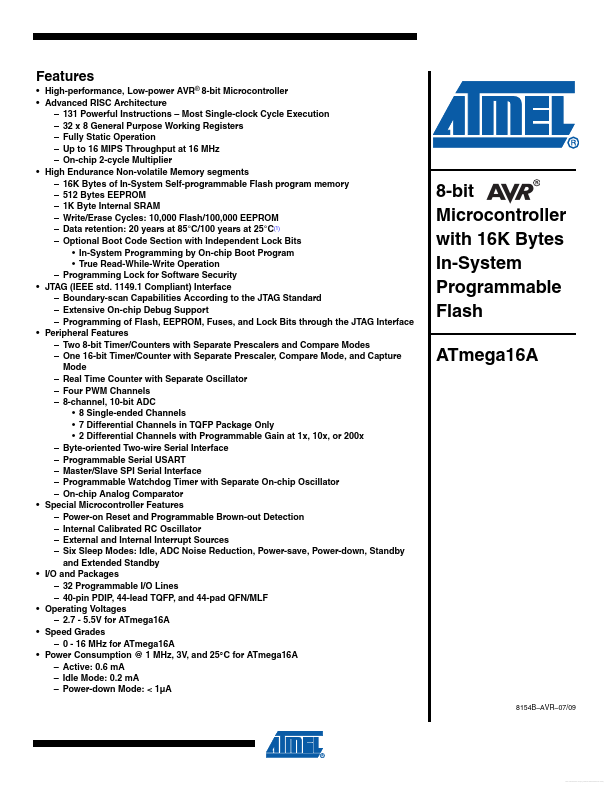

ATMEGA16A Overview

Key Specifications

Mount Type: Surface Mount

Pins: 44

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 2.7 V

Key Features

- High-performance, Low-power AVR® 8-bit Microcontroller

- In-System Programming by On-chip Boot Program

- 8 Single-ended Channels

- 7 Differential Channels in TQFP Package Only