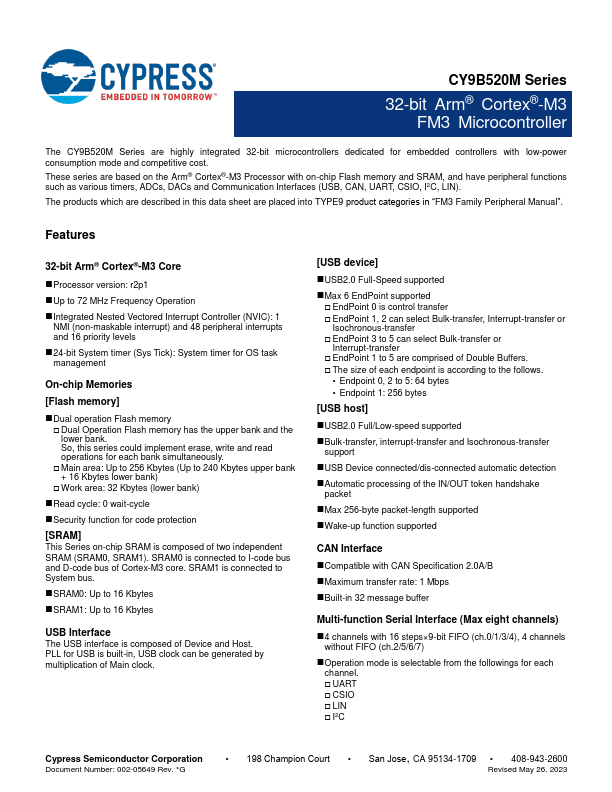

CY9BF521L Overview

Key Features

- Processor version: r2p1

- Up to 72 MHz Frequency Operation

- Integrated Nested Vectored Interrupt Controller (NVIC): 1 NMI (non-maskable interrupt) and 48 peripheral interrupts and 16 priority levels

- 24-bit System timer (Sys Tick): System timer for OS task management On-chip Memories [Flash memory]

- Read cycle: 0 wait-cycle

- SRAM0: Up to 16 Kbytes

- USB2.0 Full-Speed supported