Description

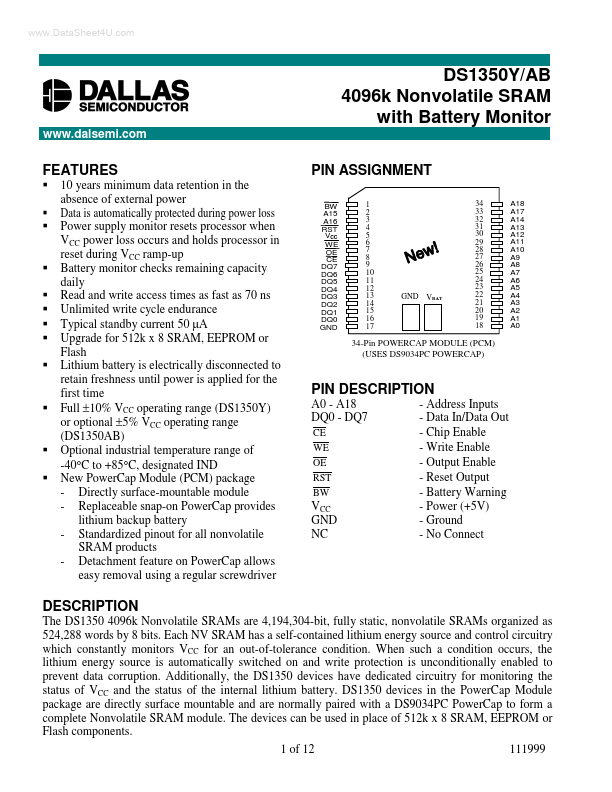

A0 - A18 DQ0 - DQ7

CE WE OE RST BW

VCC GND NC

- Address Inputs - Data In/Data Out - Chip Enable - Write Enable - Output Enable - Reset Output - Battery Warning - Power (+5V) - Ground - No Connect

DESCRIPTION

The DS1350 4096k Nonvolatile SRAMs are 4,194,304-bit, fully static, nonvolatile SRAMs organized as 524,288 words by 8 bits.Each NV SRAM has a self-contained lithium energy source and control circuitry which constantly monitors VCC for an out-of-tolerance condition.When such a condition

Features

- 10 years minimum data retention in the absence of external power Data is automatically protected during power loss Power supply monitor resets processor when VCC power loss occurs and holds processor in reset during VCC ramp-up Battery monitor checks remaining capacity daily Read and write access times as fast as 70 ns Unlimited write cycle endurance Typical standby current 50 µA Upgrade for 512k x 8 SRAM, EEPROM or Flash Lithium battery is electrically disconnected to retain freshness until pow.