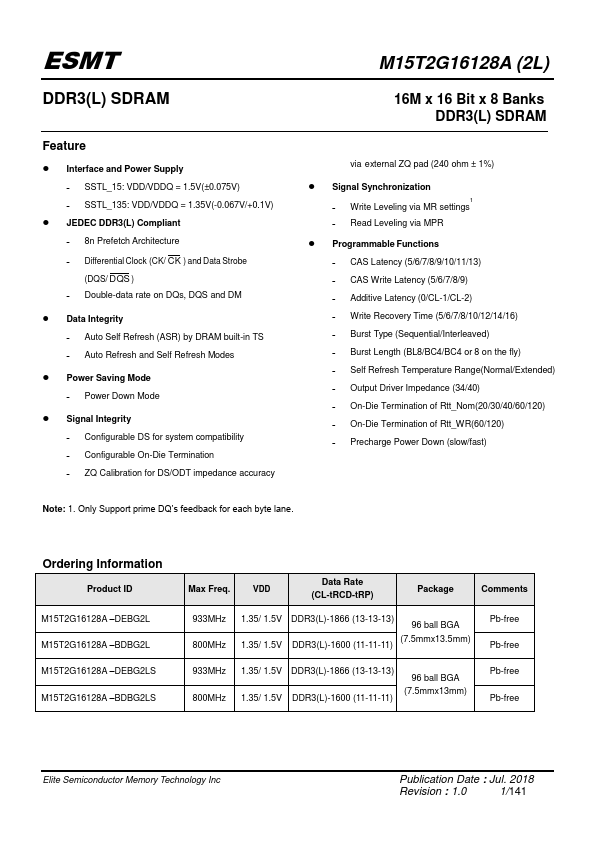

M15T2G16128A

Description

The 2Gb Double-Data-Rate-3(L) (DDR3(L)) DRAM is double data rate architecture to achieve high-speed operation.

Key Features

- Data Integrity ˗ Auto Self Refresh (ASR) by DRAM built-in TS ˗ Auto Refresh and Self Refresh Modes

- Power Saving Mode ˗ Power Down Mode

- Signal Synchronization 1 ˗ Write Leveling via MR settings ˗ Read Leveling via MPR

- Only Support prime DQ’s feedback for each byte lane