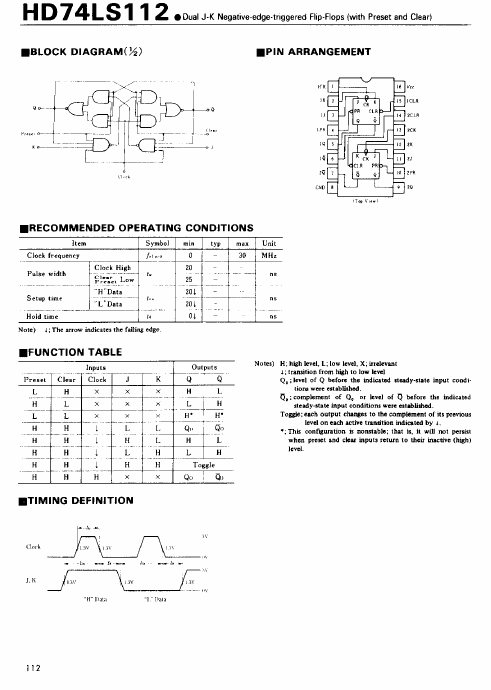

74LS112

19.20 20.00 Max 16 9 7.40 Max 6.30

Unit: mm

1 1.3

1.11 Max

0.51 Min

2.54 Min 5.06 Max

2.54 ± 0.25

0.48 ± 0.10

- 0.05 0°

- 15°

Hitachi Code JEDEC EIAJ Weight (reference value)

+ 0.13

DP-16 Conforms Conforms 1.07 g

Unit: mm

10.06 10.5 Max 16 9

- 0.22 ± 0.05 0.20 ± 0.04

8 0.80 Max

2.20 Max

0.20 7.80 +

- 0.30

1.15 0°

- 8° 0.70 ± 0.20

- 0.42 ± 0.08 0.40 ± 0.06

0.12 M

Hitachi Code JEDEC EIAJ Weight (reference value) FP-16DA

- Conforms 0.24 g

- Dimension including the plating thickness Base material dimension

0.10 ± 0.10

Unit: mm

9.9 10.3 Max 16 9 3.95 1 1.27 0.635 Max 8

0.11 0.14 +

- 0.04 1.75 Max

- 0.22 ± 0.03 0.20 ±...