Description

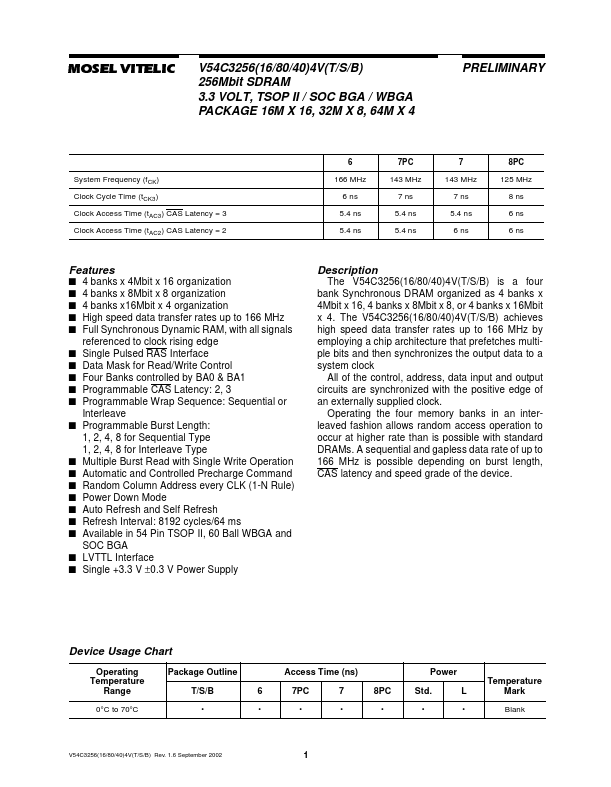

The V54C3256(16/80/40)4V(T/S/B) is a four bank Synchronous DRAM organized as 4 banks x 4Mbit x 16, 4 banks x 8Mbit x 8, or 4 banks x 16Mbit x 4.

Features

- 4 banks x 4Mbit x 16 organization 4 banks x 8Mbit x 8 organization 4 banks x16Mbit x 4 organization High speed data transfer rates up to 166 MHz Full Synchronous Dynamic RAM, with all signals referenced to clock rising edge Single Pulsed RAS Interface Data Mask for Read/Write Control Four Banks controlled by BA0 & BA1 Programmable CAS Latency: 2, 3 Programmable Wrap Sequence: Sequential or Interleave Programmable Burst Length: 1,.

V54-C32.pdf

V54-C32.pdf