Description

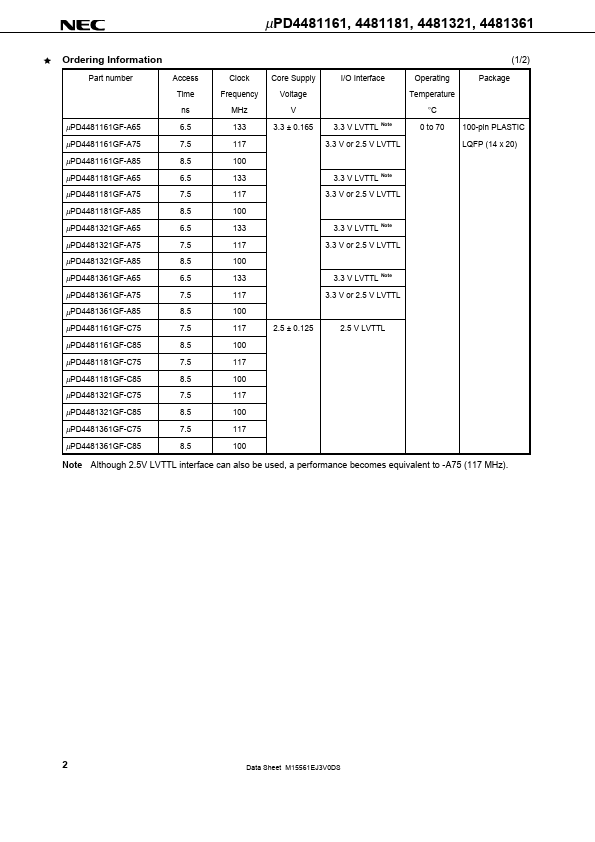

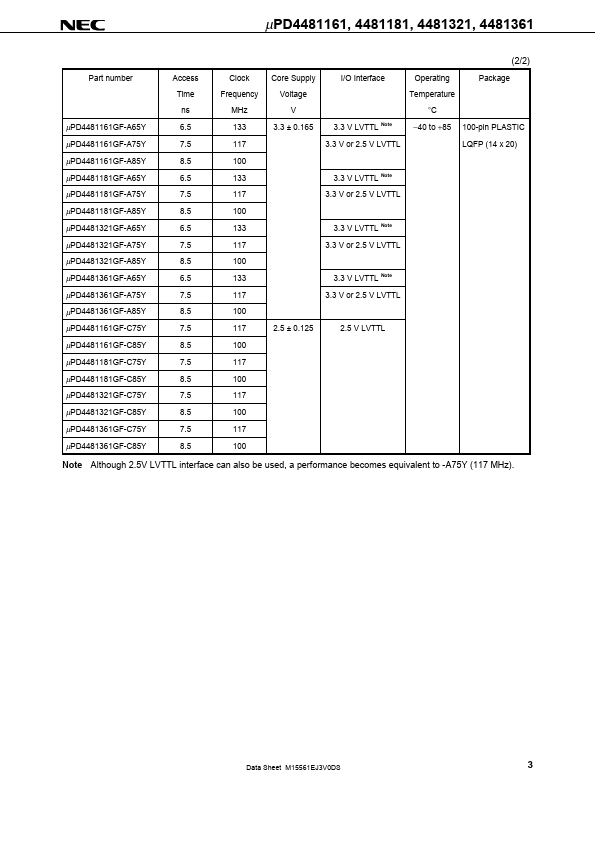

The µPD4481161 is a 524,288-word by 16-bit, the µPD4481181 is a 524,288-word by 18-bit, the µPD4481321 is a 262,144-word by 32-bit and the µPD4481361 is a 262,144-word by 36-bit ZEROSB static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell.

Features

- Low voltage core supply : VDD = 3.3 ± 0.165 V (-A65, -A75, -A85, -A65Y, -A75Y, -A85Y) VDD = 2.5 ± 0.125 V (-C75, -C85, -C75Y, -C85Y).

- Synchronous operation.

- Operating temperature : TA = 0 to 70 °C (-A65, -A75, -A85, -C75, -C85) TA =.

- 40 to +85 °C (-A65Y, -A75Y, -A85Y, -C75Y, -C85Y).

- 100 percent bus utilization.

- Internally self-timed write control.

- Burst read / write : Interleaved burst and linear burst sequence.

- Fully regist.