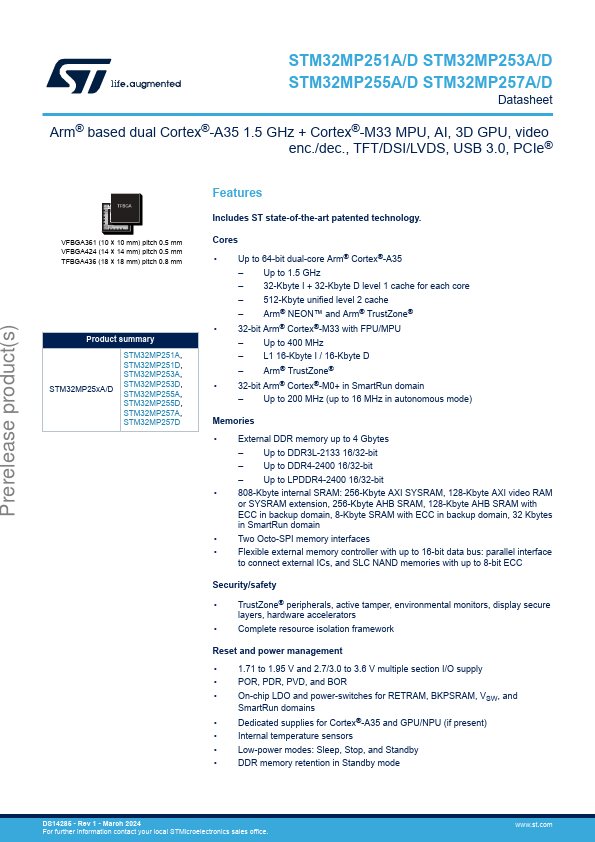

STM32MP257A Overview

Key Specifications

Key Features

- 32-bit Arm® Cortex®-M33 with FPU/MPU – Up to 400 MHz – L1 16-Kbyte I / 16-Kbyte D – Arm® TrustZone®

- 32-bit Arm® Cortex®-M0+ in SmartRun domain – Up to 200 MHz (up to 16 MHz in autonomous mode) Memories

- Two Octo-SPI memory interfaces

- TrustZone® peripherals, active tamper, environmental monitors, display secure layers, hardware accelerators

- Complete resource isolation framework Reset and power management