VDS8608A8A

VDS8608A8A is Synchronous DRAM manufactured by A-Data Technology.

- Part of the VDS8608A8A_A comparator family.

- Part of the VDS8608A8A_A comparator family.

V-Data

Synchronous DRAM

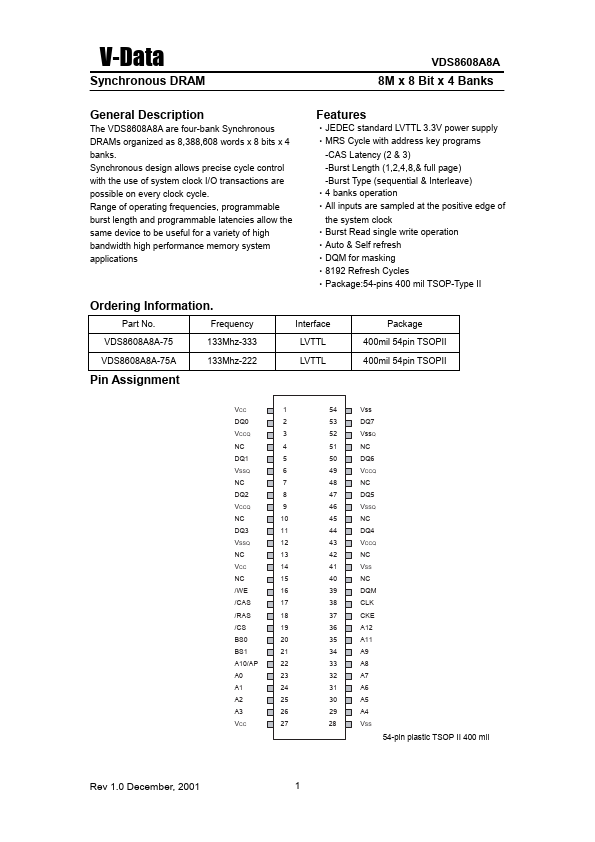

VDS8608A8A 8M x 8 Bit x 4 Banks

General Description

The VDS8608A8A are four-bank Synchronous DRAMs organized as 8,388,608 words x 8 bits x 4 banks. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth high performance memory system applications

Features

- JEDEC standard LVTTL 3.3V power supply

- MRS Cycle with address key programs

-CAS Latency (2 & 3) -Burst Length (1,2,4,8,& full page) -Burst Type (sequential & Interleave)

- 4 banks...