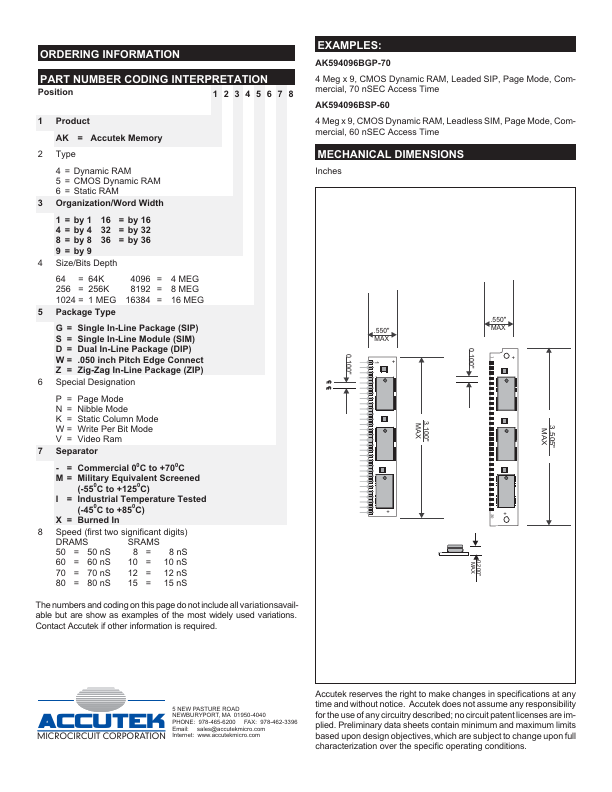

Datasheet Summary

MICROCIRCUIT CORPORATION

DESCRIPTION

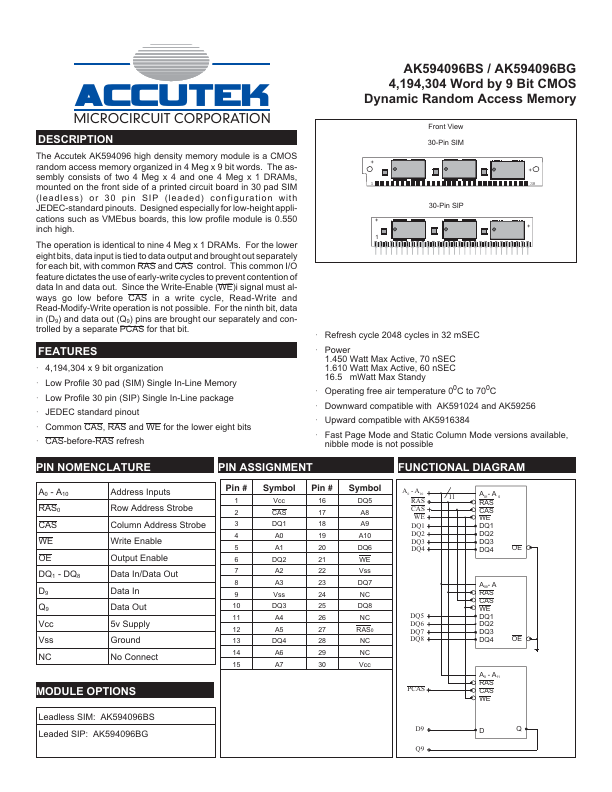

The Accutek AK594096 high density memory module is a CMOS random access memory organized in 4 Meg x 9 bit words. The assembly consists of two 4 Meg x 4 and one 4 Meg x 1 DRAMs, mounted on the front side of a printed circuit board in 30 pad SIM (leadless) or 30 pin SIP (leaded) configuration with JEDEC-standard pinouts. Designed especially for low-height applications such as VMEbus boards, this low profile module is 0.550 inch high. The operation is identical to nine 4 Meg x 1 DRAMs. For the lower eight bits, data input is tied to data output and brought out separately for each bit, with mon RAS and CAS control. This mon I/O feature dictates the...